I have been writing code since 1986.

Budapest, Europe

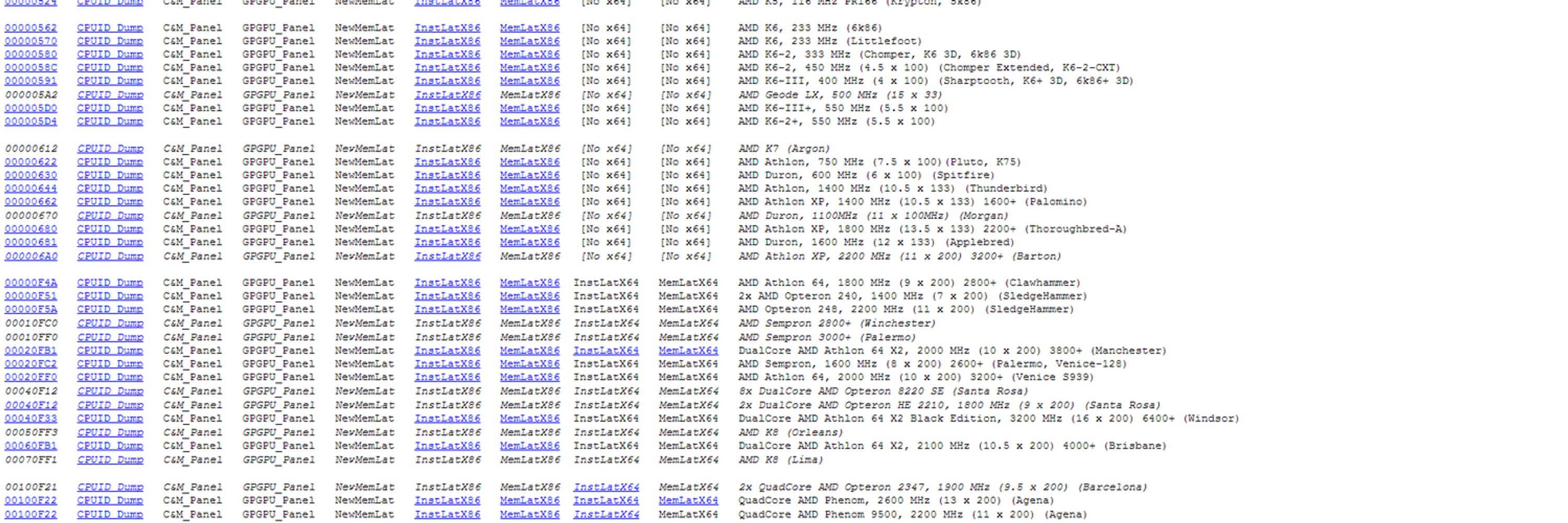

https://instlatx64.github.io/InstLatx64/

cdrdv2-public.intel.com/859022/intel...

cdrdv2-public.intel.com/859022/intel...

cdrdv2-public.intel.com/869278/TDX%2...

cdrdv2-public.intel.com/869278/TDX%2...

docs.amd.com/v/u/en-US/69...

docs.amd.com/v/u/en-US/69...

www.intel.com/content/www/...

www.intel.com/content/www/...

( #Genova #Zen4 B0 CPUID A10F11 #EPYC )

docs.amd.com/v/u/en-US/57...

( #Genova #Zen4 B0 CPUID A10F11 #EPYC )

docs.amd.com/v/u/en-US/57...

( #Bergamo #Zen4c A0 CPUID AA0F02 #EPYC )

docs.amd.com/v/u/en-US/57...

( #Bergamo #Zen4c A0 CPUID AA0F02 #EPYC )

docs.amd.com/v/u/en-US/57...

Download:

cdrdv2-public.intel.com/869288/31943...

#DiamondRapids #NovaLake #WildcatLake #PantherCove #CoyoteCove #ArcticWolf

Download:

cdrdv2-public.intel.com/869288/31943...

#DiamondRapids #NovaLake #WildcatLake #PantherCove #CoyoteCove #ArcticWolf

#AVX512QVNNI - byte form of 4VNNIW, it would extinct with KNM/MIC;

#AVX512DFMA - VDF[,n]MADD[P,S][S,D] - I have no idea what the difference between FMA & DFMA;

#AVX512BITALG2 - this is the most interesting for me;

1/3

#AVX512QVNNI - byte form of 4VNNIW, it would extinct with KNM/MIC;

#AVX512DFMA - VDF[,n]MADD[P,S][S,D] - I have no idea what the difference between FMA & DFMA;

#AVX512BITALG2 - this is the most interesting for me;

1/3

#AMD #Intel #Zen6 #AVX10_2 #AVX_VNNI #AVX_VNNI_INT8 #AVX_VNNI_INT16 #DiamondRapids #NovaLake

#AMD #Intel #Zen6 #AVX10_2 #AVX_VNNI #AVX_VNNI_INT8 #AVX_VNNI_INT16 #DiamondRapids #NovaLake

www.amd.com/en/resources...

www.amd.com/en/resources...

cdrdv2-public.intel.com/868911/D5139...

cdrdv2-public.intel.com/868911/D5139...

All-in-One:

cdrdv2-public.intel.com/868137/32546...

Changes v81:

cdrdv2-public.intel.com/868136/25204...

UDB (opcode D6h) canonized

All-in-One:

cdrdv2-public.intel.com/868137/32546...

Changes v81:

cdrdv2-public.intel.com/868136/25204...

UDB (opcode D6h) canonized

#OCP2025 #AMD #x86EAG

www.amd.com/en/blogs/202...

youtu.be/Z36PjXFBmig?...

#OCP2025 #AMD #x86EAG

www.amd.com/en/blogs/202...

youtu.be/Z36PjXFBmig?...

Probably just a documentation bug.

cdrdv2-public.intel.com/867556/intel...

Probably just a documentation bug.

cdrdv2-public.intel.com/867556/intel...

nasm.us

#AVX10_2 #AVX10_VNNI_INT #APX #AMX_FP8 #AMX_TF32 #AMX_COMPLEX #AMX_AVX512 #AMX_MOVRS

nasm.us

#AVX10_2 #AVX10_VNNI_INT #APX #AMX_FP8 #AMX_TF32 #AMX_COMPLEX #AMX_AVX512 #AMX_MOVRS

cdrdv2-public.intel.com/866623/xeon-...

#Darkmont #Intel18A #LGA7529