#LEC #LEQ #Aborts

#DV #Testcase #BuildTime

#DV #Testcase #BuildTime

#PDE #DFT #ATE

chipress.online/tag/cache-co...

#Cache #CacheCoherency #MemoryModels

chipress.online/tag/cache-co...

#Cache #CacheCoherency #MemoryModels

Sometimes we may see false failures of SVAs using gated clock. We will discuss how to resolve these false failures in this post.

#SVA #ClockGating #FV

Sometimes we may see false failures of SVAs using gated clock. We will discuss how to resolve these false failures in this post.

#SVA #ClockGating #FV

#ValidReady #staller #simulation #DV

#ValidReady #staller #simulation #DV

#Cache #CacheCoherence #CoherenceConflict #FalseSharing

#Cache #CacheCoherence #CoherenceConflict #FalseSharing

#Cache #CacheCoherence

#Cache #CacheCoherence

Check it out if you are interested!

#CacheCoherency #Cache #Atomic

Check it out if you are interested!

#CacheCoherency #Cache #Atomic

#Cachef="/hashtag/CacheCoherency" class="hover:underline text-blue-600 dark:text-sky-400 no-card-link">#CacheCoherency #Cache #MSI #Snoop

#Cachef="/hashtag/CacheCoherency" class="hover:underline text-blue-600 dark:text-sky-400 no-card-link">#CacheCoherency #Cache #MSI #Snoop

www.anthropic.com/engineering/...

www.anthropic.com/engineering/...

It talks about Nvdia GPU architecture, and introduces rooflines for LLM scaling on GPUs. Check it out if you are interested.

jax-ml.github.io/scaling-book...

It talks about Nvdia GPU architecture, and introduces rooflines for LLM scaling on GPUs. Check it out if you are interested.

jax-ml.github.io/scaling-book...

#Cachef="/hashtag/CacheCoherency" class="hover:underline text-blue-600 dark:text-sky-400 no-card-link">#CacheCoherency #Cache #MSI #Snoop

#Cachef="/hashtag/CacheCoherency" class="hover:underline text-blue-600 dark:text-sky-400 no-card-link">#CacheCoherency #Cache #MSI #Snoop

#Cachef="/hashtag/CacheCoherency" class="hover:underline text-blue-600 dark:text-sky-400 no-card-link">#CacheCoherency #Cache #MSI #Snoop

Using linear algebra is another interesting comparator-free sorting solution. Check it out!

#ASIC #RTL #Sorting #Sort

chipress.online/2024/05/01/h...

Using linear algebra is another interesting comparator-free sorting solution. Check it out!

#ASIC #RTL #Sorting #Sort

chipress.online/2024/05/01/h...

We discussed hardware implementation for array sorting using comparators. However, it is also possible to sort arrays without comparators.

#ASIC #RTL #Sorting #Sort

chipress.online/2024/04/30/h...

We discussed hardware implementation for array sorting using comparators. However, it is also possible to sort arrays without comparators.

#ASIC #RTL #Sorting #Sort

chipress.online/2024/04/30/h...

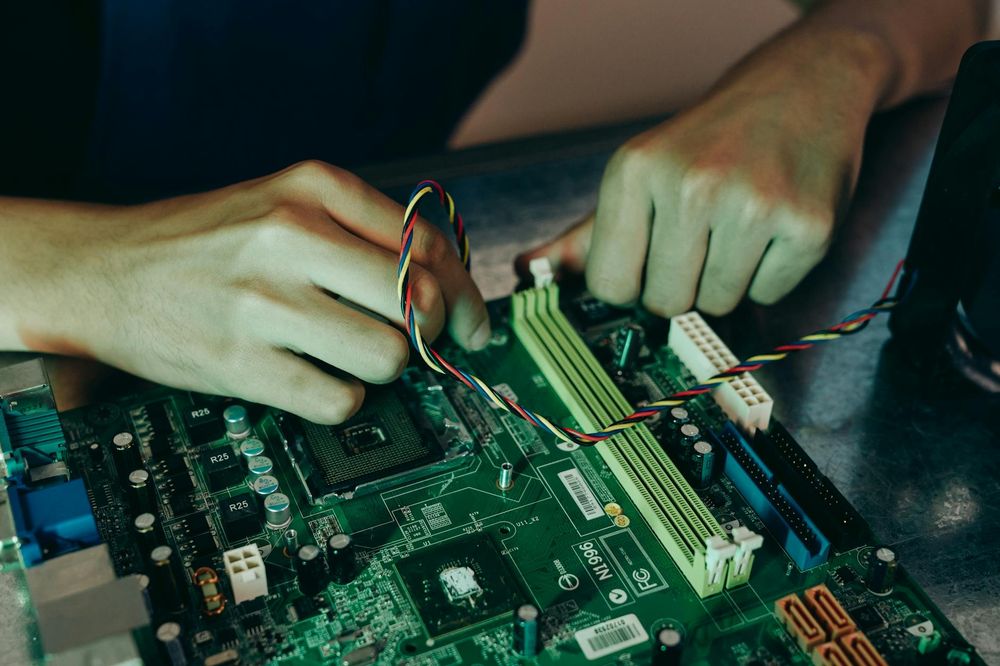

Implementing array sorting in hardware is a hot interview topic for high frequency trading companies. Software based sorting can be leveraged by hardware.

#ASIC #RTL #Sorting #Sort

chipress.online/2024/04/29/h...

Implementing array sorting in hardware is a hot interview topic for high frequency trading companies. Software based sorting can be leveraged by hardware.

#ASIC #RTL #Sorting #Sort

chipress.online/2024/04/29/h...

In real-world cache coherence implementation, designers must properly handle non-atomic operations. This is often overlooked, and we'll expand this topic in detail.

#CacheCoherency #Cache #MSI #Snoop

In real-world cache coherence implementation, designers must properly handle non-atomic operations. This is often overlooked, and we'll expand this topic in detail.

#CacheCoherency #Cache #MSI #Snoop

In this post, we share a few must-read list of papers for ASIC design interviews. You might find these papers helpful in your interview preparations.

#ASIC #SOC #RTL #Interview

In this post, we share a few must-read list of papers for ASIC design interviews. You might find these papers helpful in your interview preparations.

#ASIC #SOC #RTL #Interview

#Power #PowerAnalysis #PowerEstimation

#Power #PowerAnalysis #PowerEstimation

#LLM #AI

#Cachef="/hashtag/CacheCoherency" class="hover:underline text-blue-600 dark:text-sky-400 no-card-link">#CacheCoherency #Cache #MemoryModel

#Cachef="/hashtag/CacheCoherency" class="hover:underline text-blue-600 dark:text-sky-400 no-card-link">#CacheCoherency #Cache #MemoryModel