Bitman6502

@afachat.bsky.social

IT-Architect and Retro-Computing Hobbyist.

See http://www.6502.org/users/andre/index.html and https://extrapages.de/

See http://www.6502.org/users/andre/index.html and https://extrapages.de/

I'm still looking for a (working!) tool that limits the CPU freq automatically once a temperature limit has been reached.

September 27, 2025 at 11:54 AM

I'm still looking for a (working!) tool that limits the CPU freq automatically once a temperature limit has been reached.

I actually finally seem to have found a tool to effectively limit the CPU speed and thus avoid overheating....

September 27, 2025 at 11:53 AM

I actually finally seem to have found a tool to effectively limit the CPU speed and thus avoid overheating....

For being newbie, a great start! I didn't notice!

Btw on my mobile, the site banner isn't even showing!

Btw on my mobile, the site banner isn't even showing!

September 12, 2025 at 5:14 AM

For being newbie, a great start! I didn't notice!

Btw on my mobile, the site banner isn't even showing!

Btw on my mobile, the site banner isn't even showing!

Advertised an article on the Amiga with a picture of an IBM PC? That isn't even in the article as far as I can see?

Please....!

Please....!

September 11, 2025 at 10:43 PM

Advertised an article on the Amiga with a picture of an IBM PC? That isn't even in the article as far as I can see?

Please....!

Please....!

caching changes is basically tracking deltas (if you don't want to compare the whole model on save - that depends on the model size) and a difference only comes in if consecutive changes affect the same parts of the model.2/2

August 15, 2025 at 9:10 AM

caching changes is basically tracking deltas (if you don't want to compare the whole model on save - that depends on the model size) and a difference only comes in if consecutive changes affect the same parts of the model.2/2

That's another option. You need to weigh in the size of the model, the total runtime, the number of changes per runtime, and how many changes affect the same part of the model. The latter is probably the most important. 1/2

August 15, 2025 at 9:10 AM

That's another option. You need to weigh in the size of the model, the total runtime, the number of changes per runtime, and how many changes affect the same part of the model. The latter is probably the most important. 1/2

If you have a deterministic model, you only need to save the changes to it in case you do changes. Might be much less data, possibly depending on the amount of erosion. But probably better to compress anyway

August 15, 2025 at 7:54 AM

If you have a deterministic model, you only need to save the changes to it in case you do changes. Might be much less data, possibly depending on the amount of erosion. But probably better to compress anyway

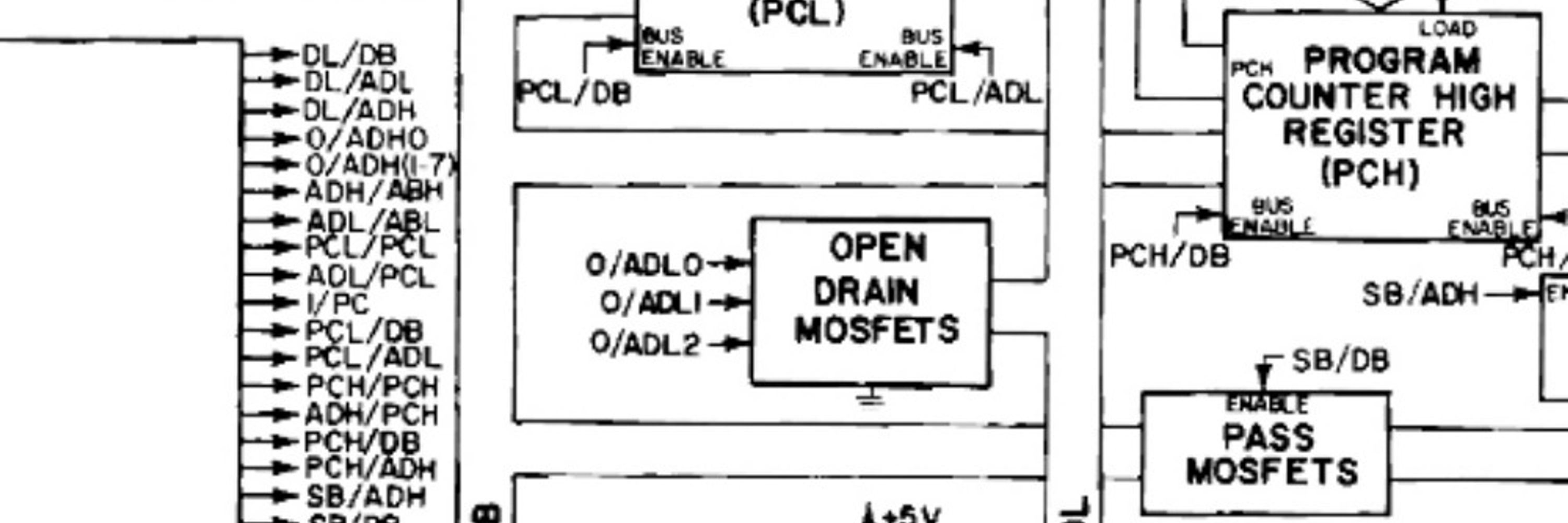

Actually just know how to build logic circuits from logic equations and registers. And then you just need to learn the formalisms like syntax

July 25, 2025 at 10:31 AM

Actually just know how to build logic circuits from logic equations and registers. And then you just need to learn the formalisms like syntax

Basically VHDL is a way to describe logic equations and registers - basic logic stuff. And most of my VHDL is just like that. The rest is compiler magic

July 25, 2025 at 10:30 AM

Basically VHDL is a way to describe logic equations and registers - basic logic stuff. And most of my VHDL is just like that. The rest is compiler magic

There are certain limitations regarding memory bandwidth that actually made me use C64 like sprites as well. The sprite info needs to be fetched in time, and there are only so many off screen cycles available...

July 24, 2025 at 7:06 PM

There are certain limitations regarding memory bandwidth that actually made me use C64 like sprites as well. The sprite info needs to be fetched in time, and there are only so many off screen cycles available...

Oh, you're asking about the 'code'? I meant VHDL code I use to program the FPGA

July 24, 2025 at 7:04 PM

Oh, you're asking about the 'code'? I meant VHDL code I use to program the FPGA

Yes it's FPGA. But you need to control the video output, esp if you want to be somewhat compatible with the PET's CRTC chip with its flexible screen geometry. So, you can use it like a CRTC for most parts, with additional registers similar to the VDC and VIC-II

July 24, 2025 at 7:03 PM

Yes it's FPGA. But you need to control the video output, esp if you want to be somewhat compatible with the PET's CRTC chip with its flexible screen geometry. So, you can use it like a CRTC for most parts, with additional registers similar to the VDC and VIC-II

The video resolution is fixed either VGA 720x576p50 or 720x480p60 (or half framerate for TV compat.) The PET CRTC can produce various screen geometries, with 320/640x200 by default. Those are just put into that 720x576 box ('frame canvas' maybe my wording isn't ideal), with the rest being border.

July 24, 2025 at 7:01 PM

The video resolution is fixed either VGA 720x576p50 or 720x480p60 (or half framerate for TV compat.) The PET CRTC can produce various screen geometries, with 320/640x200 by default. Those are just put into that 720x576 box ('frame canvas' maybe my wording isn't ideal), with the rest being border.