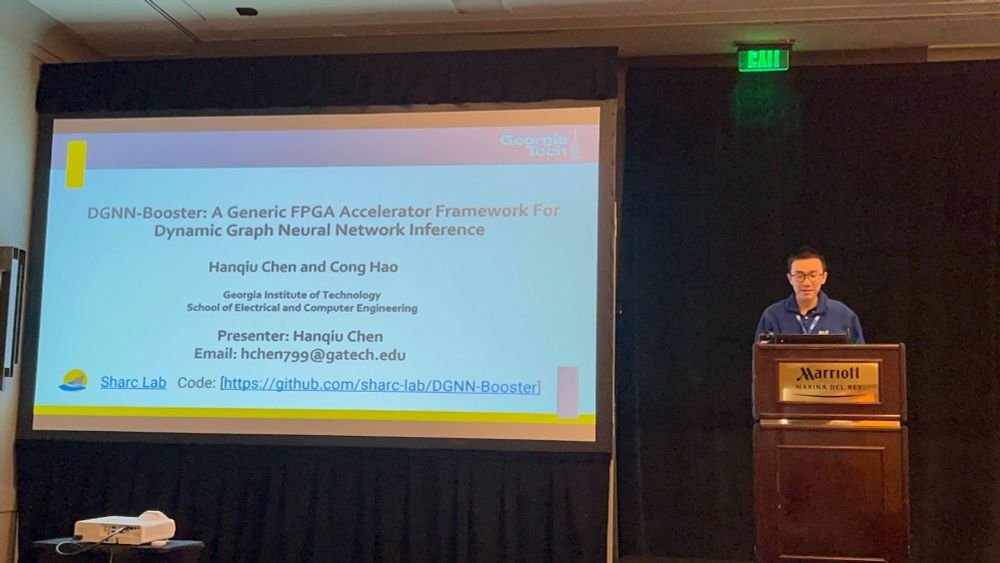

Sharc Lab @ Georgia Tech

@sharclab.bsky.social

Software/Hardware Co-Design for Intelligence and Efficiency (Sharc) Lab @ Georgia Tech

Atlanta, Georgia, USA

sharclab.ece.gatech.edu

Atlanta, Georgia, USA

sharclab.ece.gatech.edu

Reposted by Sharc Lab @ Georgia Tech

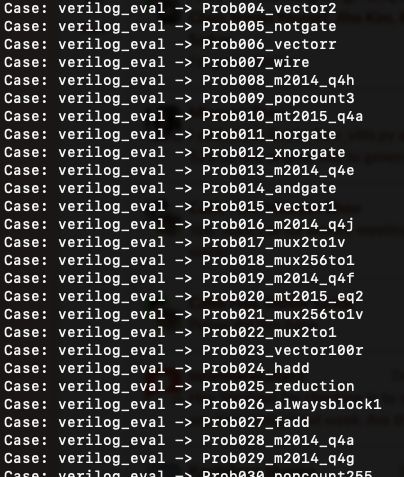

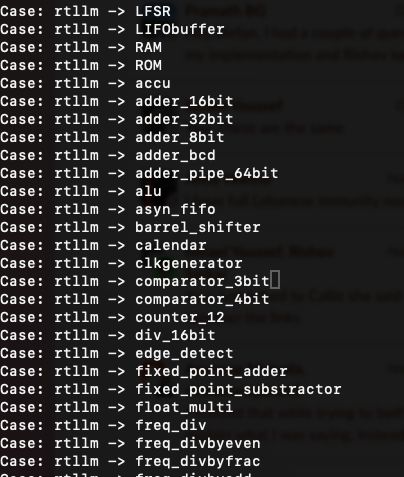

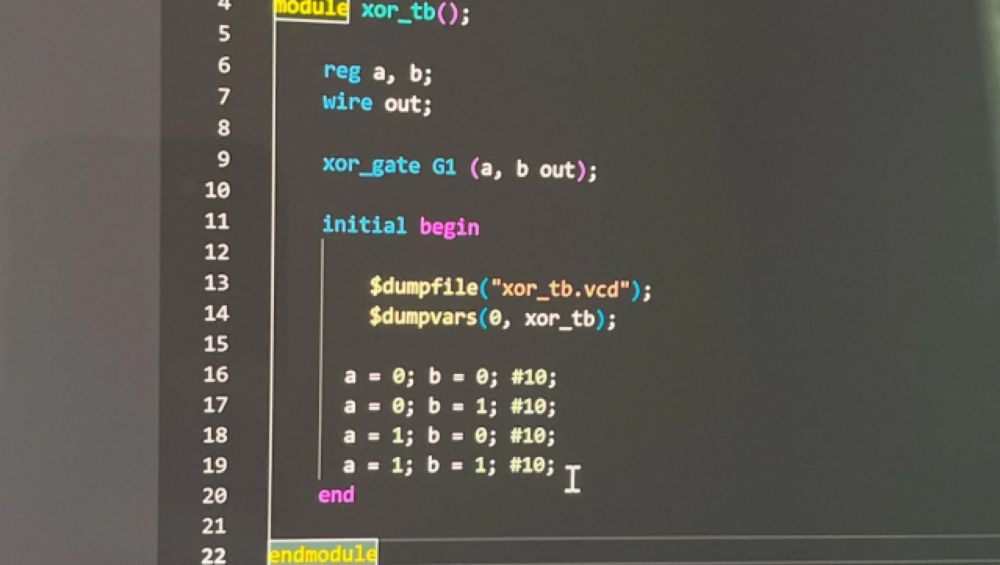

Verilog-Eval and RTLLM go brrr...

Finally working with local LLM inference after some bugs with vLLM

Finally working with local LLM inference after some bugs with vLLM

January 8, 2025 at 1:03 AM

Verilog-Eval and RTLLM go brrr...

Finally working with local LLM inference after some bugs with vLLM

Finally working with local LLM inference after some bugs with vLLM

Reposted by Sharc Lab @ Georgia Tech

Shoutout to when I discovered that in Xilinx’s Vitis HLS 2023.1, the “help” command causes a segfault

November 30, 2024 at 11:54 PM

Shoutout to when I discovered that in Xilinx’s Vitis HLS 2023.1, the “help” command causes a segfault

Reposted by Sharc Lab @ Georgia Tech

Anytime a new version of any chip design / EDA tool is released

November 30, 2024 at 11:48 PM

Anytime a new version of any chip design / EDA tool is released

Reposted by Sharc Lab @ Georgia Tech

Here's a short preview of a paper that Quentin Corradi, my PhD student with George Constantinides, will be presenting in the FUZZING'24 workshop at ISSTA next week... johnwickerson.wordpress.com/2024/09/09/a...

Automated feature testing of Verilog parsers using fuzzing

I'm delighted that Quentin Corradi, a PhD student I jointly supervise with George Constantinides, will be presenting his work to improve the reliability of hardware design tools next week at the FUZZI...

johnwickerson.wordpress.com

September 9, 2024 at 2:28 PM

Here's a short preview of a paper that Quentin Corradi, my PhD student with George Constantinides, will be presenting in the FUZZING'24 workshop at ISSTA next week... johnwickerson.wordpress.com/2024/09/09/a...

Reposted by Sharc Lab @ Georgia Tech

Took my research group out this week: current members and cosupervisors who could make it. One of the key privileges of working at Imperial College is the great early career researchers you get to work with.

November 21, 2024 at 5:21 PM

Took my research group out this week: current members and cosupervisors who could make it. One of the key privileges of working at Imperial College is the great early career researchers you get to work with.

As graduate students and avid PowerPoint users, we often encounter the most bizarre PowerPoint bugs. Recently, our PhD student, Risohv, found that emojis larger than 60pt with text shadows cause significant lag in PowerPoint. Emojis under 60pt or without shadows work fine.

November 22, 2024 at 4:00 PM

As graduate students and avid PowerPoint users, we often encounter the most bizarre PowerPoint bugs. Recently, our PhD student, Risohv, found that emojis larger than 60pt with text shadows cause significant lag in PowerPoint. Emojis under 60pt or without shadows work fine.

We have burned many hours debugging high-level synthesis (HLS) code with subtle "ap_fixed" casting and initialization bugs. Reminder when using HLS to always explicitly cast and initialize your "ap_fixed" numbers and add a generous amount of parentheses to make order of operations explicit. #FPGA

November 20, 2024 at 11:21 PM

We have burned many hours debugging high-level synthesis (HLS) code with subtle "ap_fixed" casting and initialization bugs. Reminder when using HLS to always explicitly cast and initialize your "ap_fixed" numbers and add a generous amount of parentheses to make order of operations explicit. #FPGA

Reminiscing back to 2023 on the first graduation of one of our earliest students, Akshay Karkal Kamath! 🎉 We are so proud of his truly budding career, currently at Apple, working on designing and implementing the next generation of chips (https://www.linkedin.com/in/akshaykamathk/).

November 20, 2024 at 4:00 PM

Reminiscing back to 2023 on the first graduation of one of our earliest students, Akshay Karkal Kamath! 🎉 We are so proud of his truly budding career, currently at Apple, working on designing and implementing the next generation of chips (https://www.linkedin.com/in/akshaykamathk/).

Reposted by Sharc Lab @ Georgia Tech

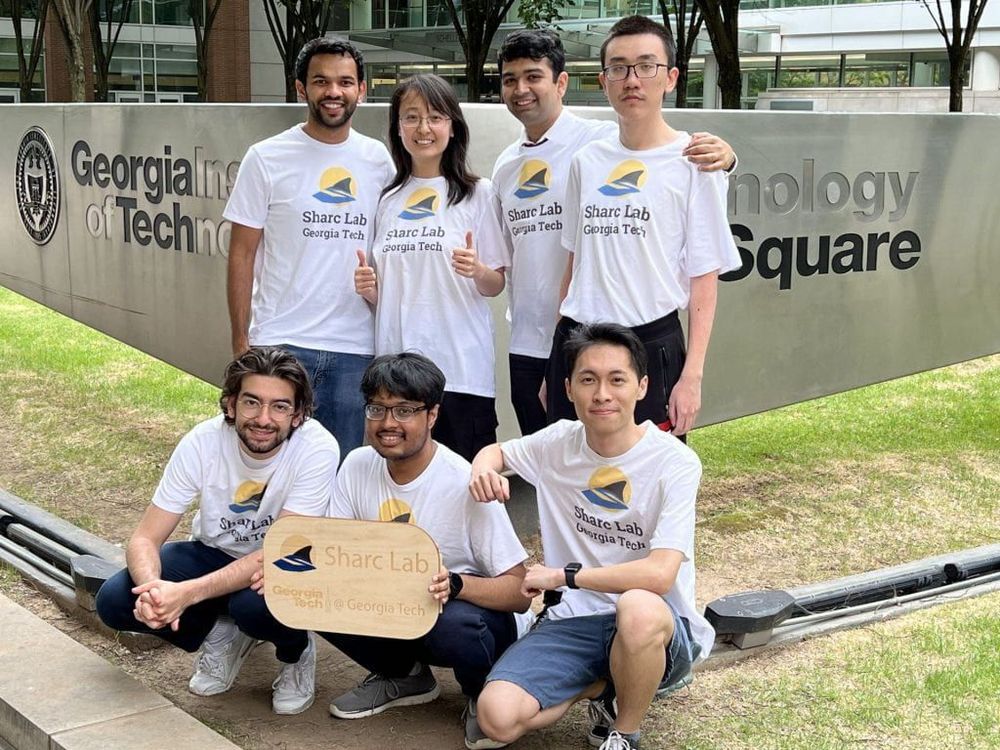

Reflecting on our 2023 lab outing on a hike followed by dinner to warmly welcome our newest PhD student at the time, Jiho Kim! ⛰️ 🏞️

November 19, 2024 at 4:00 PM

Reflecting on our 2023 lab outing on a hike followed by dinner to warmly welcome our newest PhD student at the time, Jiho Kim! ⛰️ 🏞️

Reposted by Sharc Lab @ Georgia Tech

LLNL looks to make HPC a little cloudier with Oxide's rackscale compute platform

LLNL looks to make HPC a little cloudier with Oxide's rackscale compute platform

System to serve as a proof of concept for applying API-driven automation to scientific computing

SC24 Oxide Computing's 2,500 pound (1.1 metric ton) rackscale blade servers are getting a new home at the Department of Energy's Lawrence Livermore…

dlvr.it

November 18, 2024 at 2:05 PM

LLNL looks to make HPC a little cloudier with Oxide's rackscale compute platform

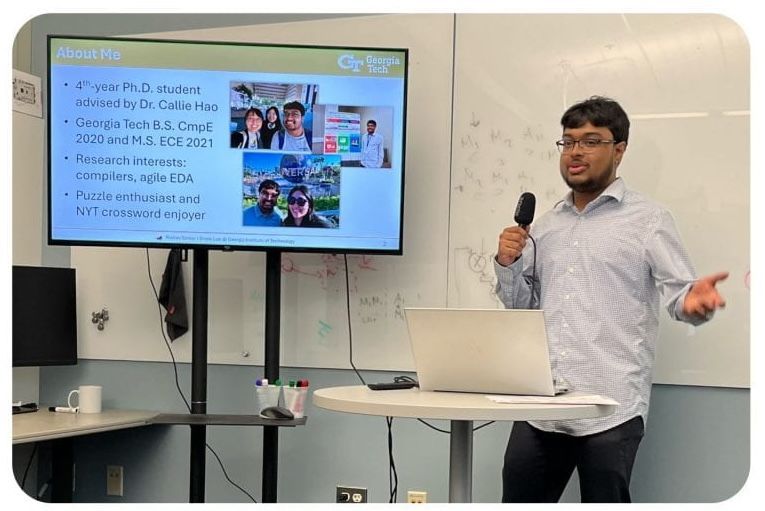

One of our first PhD students, Rishov Sarkar (@rishovsarkar.com), successfully completed his Ph.D. proposal exam! 🎉 We had dinner to celebrate the proposal and also our celebrate our newest PhD students, Andy and Ismael!

November 18, 2024 at 9:37 PM

One of our first PhD students, Rishov Sarkar (@rishovsarkar.com), successfully completed his Ph.D. proposal exam! 🎉 We had dinner to celebrate the proposal and also our celebrate our newest PhD students, Andy and Ismael!

Reposted by Sharc Lab @ Georgia Tech

Lots of discussion on copyright and AI right now. Check out Kate Downing’s #ICLR2024 Keynote on “Copyright Fundamentals for AI Researchers”. Lots of great insight there.

iclr.cc/virtual/2024...

iclr.cc/virtual/2024...

ICLR Invited Talk Copyright Fundamentals for AI ResearchersICLR 2024

iclr.cc

November 18, 2024 at 3:25 AM

Lots of discussion on copyright and AI right now. Check out Kate Downing’s #ICLR2024 Keynote on “Copyright Fundamentals for AI Researchers”. Lots of great insight there.

iclr.cc/virtual/2024...

iclr.cc/virtual/2024...

Reposted by Sharc Lab @ Georgia Tech

Hello World!

November 16, 2024 at 7:52 PM

Hello World!

Reposted by Sharc Lab @ Georgia Tech

Computing on Programmable Logic (2016):

Slides: www.microsoft.com/en-us/resear...

Video: www.youtube.com/watch?v=z1Z5...

Slides: www.microsoft.com/en-us/resear...

Video: www.youtube.com/watch?v=z1Z5...

www.microsoft.com

November 15, 2024 at 10:58 PM

Computing on Programmable Logic (2016):

Slides: www.microsoft.com/en-us/resear...

Video: www.youtube.com/watch?v=z1Z5...

Slides: www.microsoft.com/en-us/resear...

Video: www.youtube.com/watch?v=z1Z5...

Reposted by Sharc Lab @ Georgia Tech

#FPGA In 2016 I had the privilege of speaking on Computing on Programmable Logic in the ‘Computing with Exotic Technologies and Platforms’ session at the Microsoft Research Faculty Summit.

Still holds up as a primer on FPGAs and their use in compute accelerators.

fpga.org/2016/07/16/c...

Still holds up as a primer on FPGAs and their use in compute accelerators.

fpga.org/2016/07/16/c...

‘Computing on Programmable Logic’ at Microsoft Research Faculty Summit 2016

Yesterday I had the privilege of speaking on Computing on Programmable Logic (slides, video) in the ‘Computing with Exotic Technologies and Platforms’ session at the Microsoft Research …

fpga.org

November 15, 2024 at 10:56 PM

#FPGA In 2016 I had the privilege of speaking on Computing on Programmable Logic in the ‘Computing with Exotic Technologies and Platforms’ session at the Microsoft Research Faculty Summit.

Still holds up as a primer on FPGAs and their use in compute accelerators.

fpga.org/2016/07/16/c...

Still holds up as a primer on FPGAs and their use in compute accelerators.

fpga.org/2016/07/16/c...

Reposted by Sharc Lab @ Georgia Tech

OK, let's try this to show the HPC community already has momentum and can thrive here on Bluesky ...

If #HPC or #supercomputing is of interest to you, please interact with this post in some way - either repost, quote, like, reply with insights or just your fav gif, tag friends, etc.

If #HPC or #supercomputing is of interest to you, please interact with this post in some way - either repost, quote, like, reply with insights or just your fav gif, tag friends, etc.

November 13, 2024 at 11:21 PM

OK, let's try this to show the HPC community already has momentum and can thrive here on Bluesky ...

If #HPC or #supercomputing is of interest to you, please interact with this post in some way - either repost, quote, like, reply with insights or just your fav gif, tag friends, etc.

If #HPC or #supercomputing is of interest to you, please interact with this post in some way - either repost, quote, like, reply with insights or just your fav gif, tag friends, etc.

Reposted by Sharc Lab @ Georgia Tech

New Vitis HLS bug unlocked! 🔑

You cannot have multiple cpp files that have the same name in the same project even if they are in different directories

They might have updated this is never versions but who knows!

Discovered by my great lab mate @rishovsarkar.com

#xilinx #fpga

You cannot have multiple cpp files that have the same name in the same project even if they are in different directories

They might have updated this is never versions but who knows!

Discovered by my great lab mate @rishovsarkar.com

#xilinx #fpga

November 15, 2024 at 4:09 AM

New Vitis HLS bug unlocked! 🔑

You cannot have multiple cpp files that have the same name in the same project even if they are in different directories

They might have updated this is never versions but who knows!

Discovered by my great lab mate @rishovsarkar.com

#xilinx #fpga

You cannot have multiple cpp files that have the same name in the same project even if they are in different directories

They might have updated this is never versions but who knows!

Discovered by my great lab mate @rishovsarkar.com

#xilinx #fpga

Reposted by Sharc Lab @ Georgia Tech

Fun hardware design “bug” of the week: the SystemVerilog 2017 specs are not backwards compatible.

It introduces new keywords/reserved words, including “int” and “do” which appear as port names for many older designs, “int” referring to an init signal and “do” to mean “data out”.

#verilog

It introduces new keywords/reserved words, including “int” and “do” which appear as port names for many older designs, “int” referring to an init signal and “do” to mean “data out”.

#verilog

November 15, 2024 at 3:56 AM

Fun hardware design “bug” of the week: the SystemVerilog 2017 specs are not backwards compatible.

It introduces new keywords/reserved words, including “int” and “do” which appear as port names for many older designs, “int” referring to an init signal and “do” to mean “data out”.

#verilog

It introduces new keywords/reserved words, including “int” and “do” which appear as port names for many older designs, “int” referring to an init signal and “do” to mean “data out”.

#verilog

Reposted by Sharc Lab @ Georgia Tech

Prototype FPGA placer I wrote to learn Rust. Uses a really basic simulated annealing approach. Hope to integrate into an ongoing research project down the road. #fpga #eda #chipdesign

stefanabikaram.com/writing/fpga...

stefanabikaram.com/writing/fpga...

November 10, 2024 at 3:25 PM

Prototype FPGA placer I wrote to learn Rust. Uses a really basic simulated annealing approach. Hope to integrate into an ongoing research project down the road. #fpga #eda #chipdesign

stefanabikaram.com/writing/fpga...

stefanabikaram.com/writing/fpga...

Reposted by Sharc Lab @ Georgia Tech

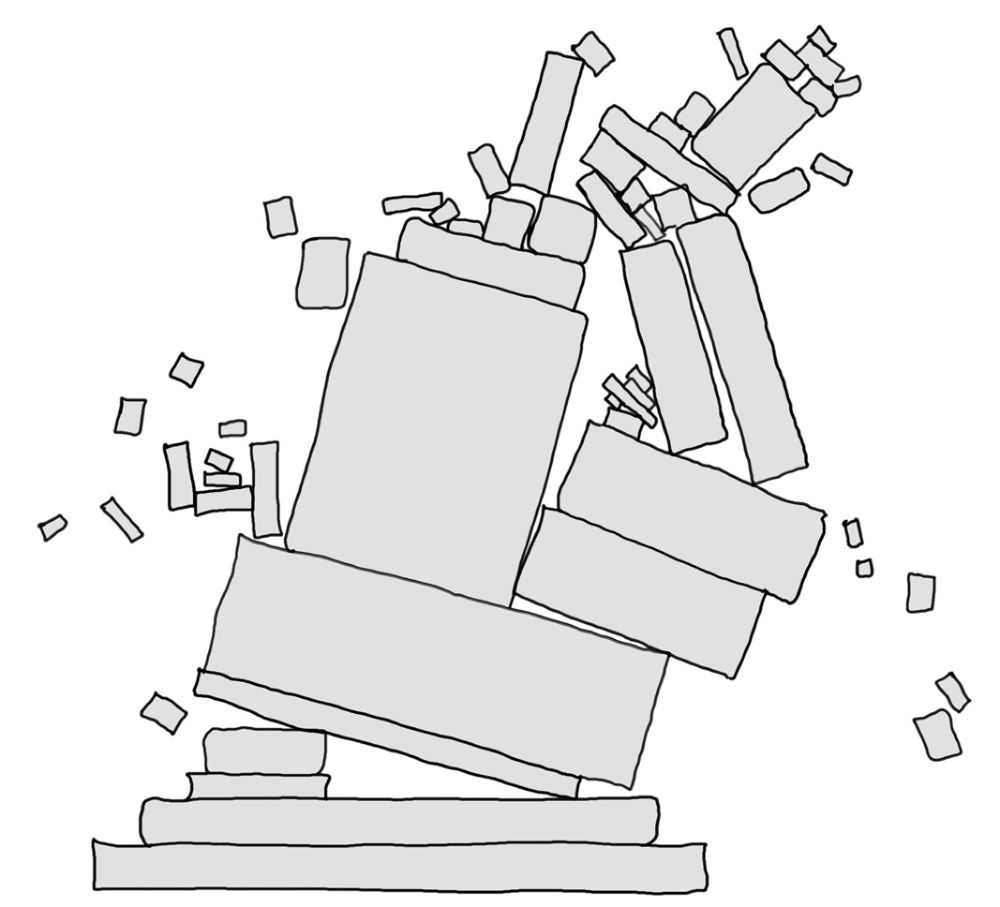

How writing HLS code feels

November 10, 2024 at 3:31 PM

How writing HLS code feels

Reposted by Sharc Lab @ Georgia Tech

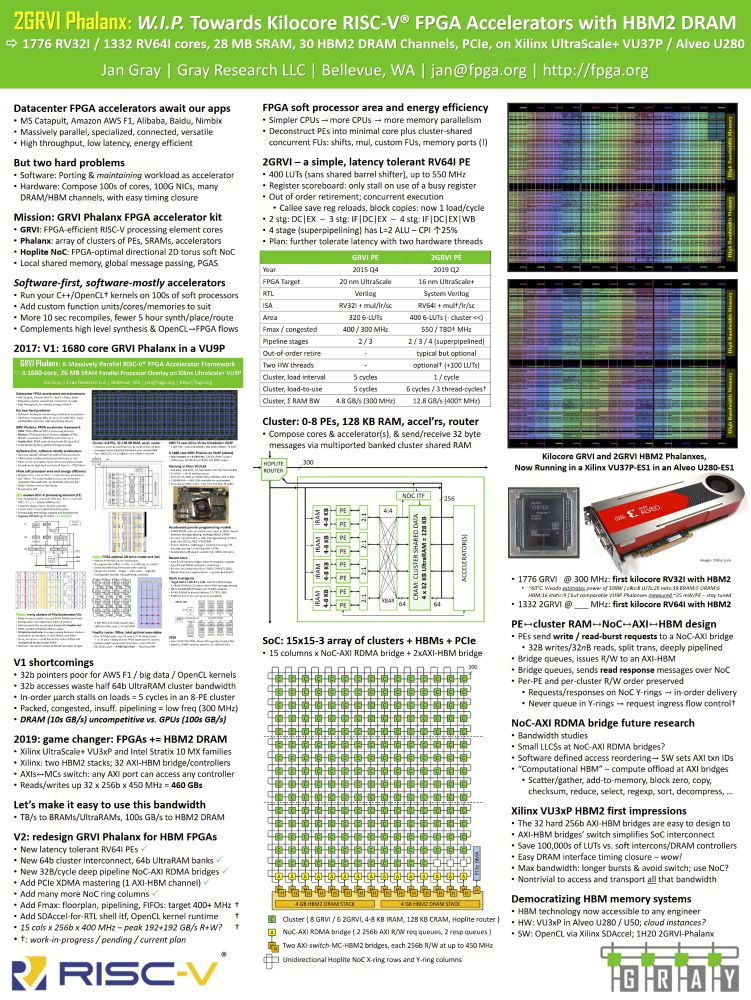

#FPGA #RISCV

2GRVI Phalanx at Hot Chips 31: The First Kilocore RISC-V RV64I with HBM2 High Bandwidth Memory

fpga.org/2019/08/19/2...

2GRVI Phalanx at Hot Chips 31: The First Kilocore RISC-V RV64I with HBM2 High Bandwidth Memory

fpga.org/2019/08/19/2...

2GRVI Phalanx at Hot Chips 31 (2019): The First Kilocore RISC-V RV64I with High Bandwidth Memory

This week at Hot Chips 31 (2019) I am presenting a status update poster on the work-in-progress GRVI Phalanx Accelerator Kit: 2GRVI Phalanx: Towards Kilocore RISC-V FPGA Accelerators with HBM2 DRAM…

fpga.org

November 12, 2024 at 4:55 AM

#FPGA #RISCV

2GRVI Phalanx at Hot Chips 31: The First Kilocore RISC-V RV64I with HBM2 High Bandwidth Memory

fpga.org/2019/08/19/2...

2GRVI Phalanx at Hot Chips 31: The First Kilocore RISC-V RV64I with HBM2 High Bandwidth Memory

fpga.org/2019/08/19/2...