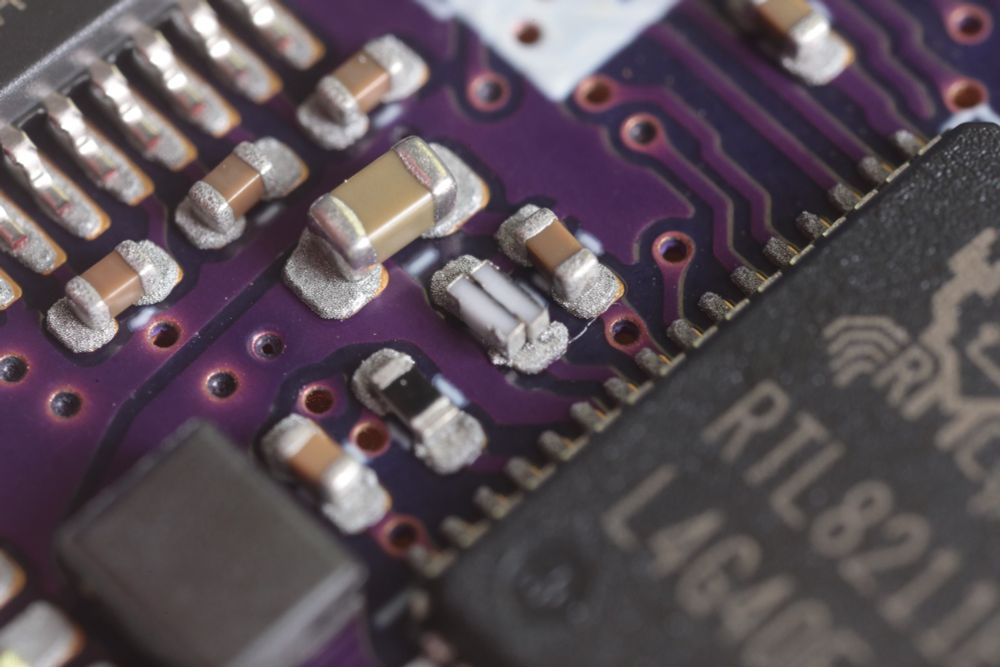

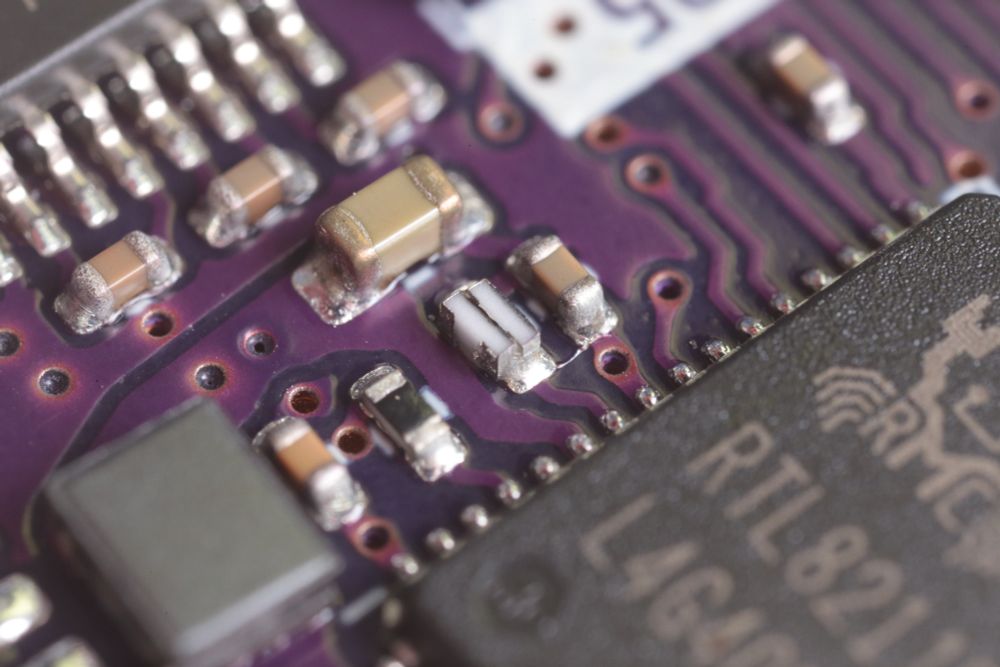

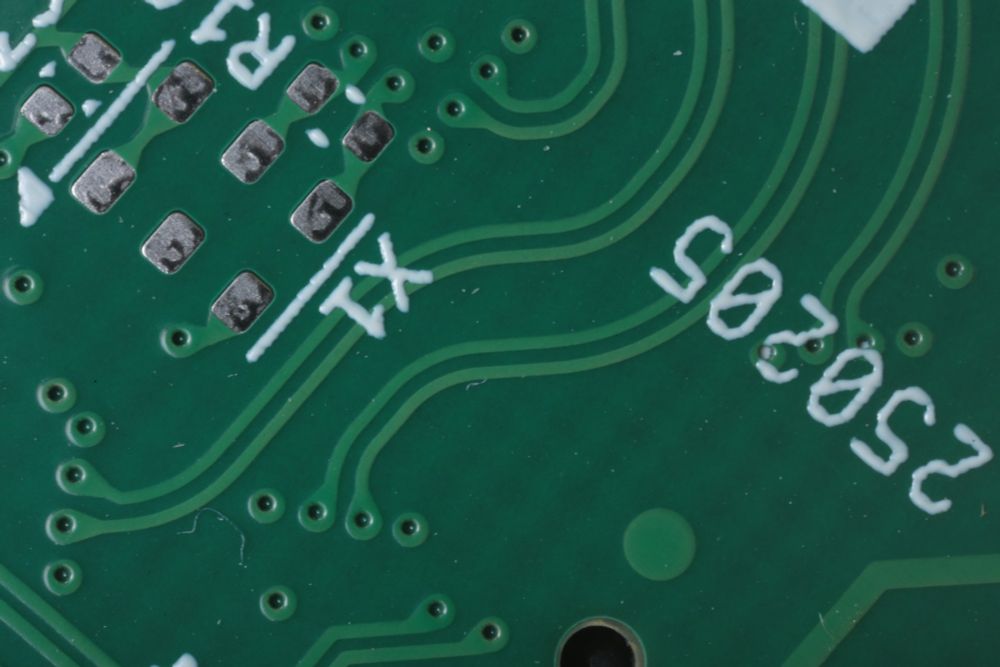

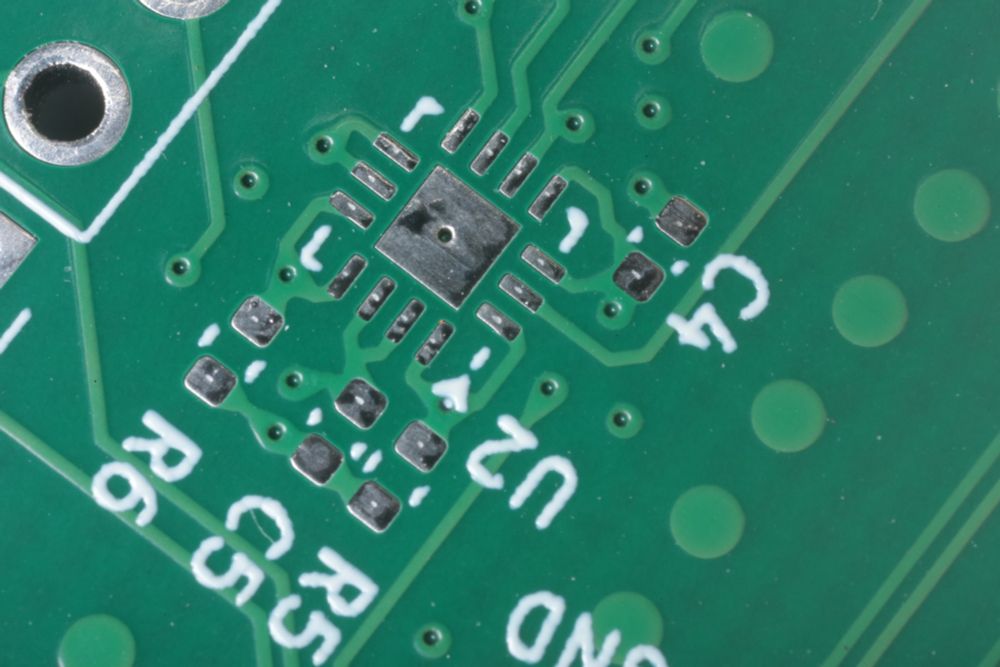

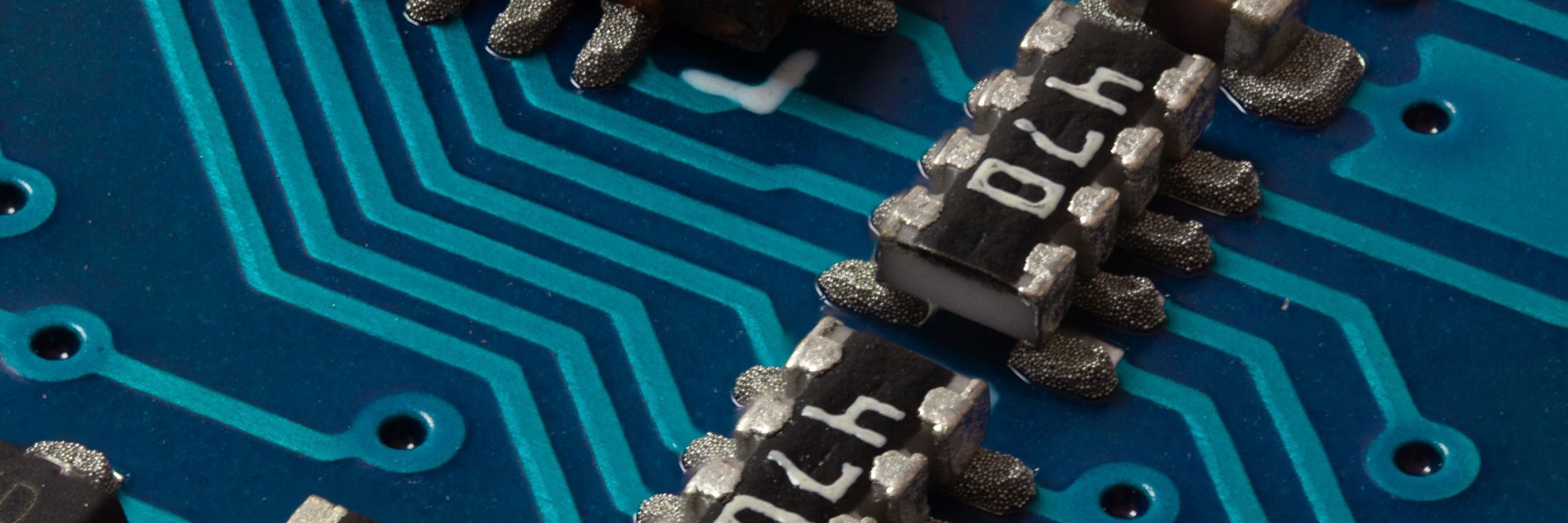

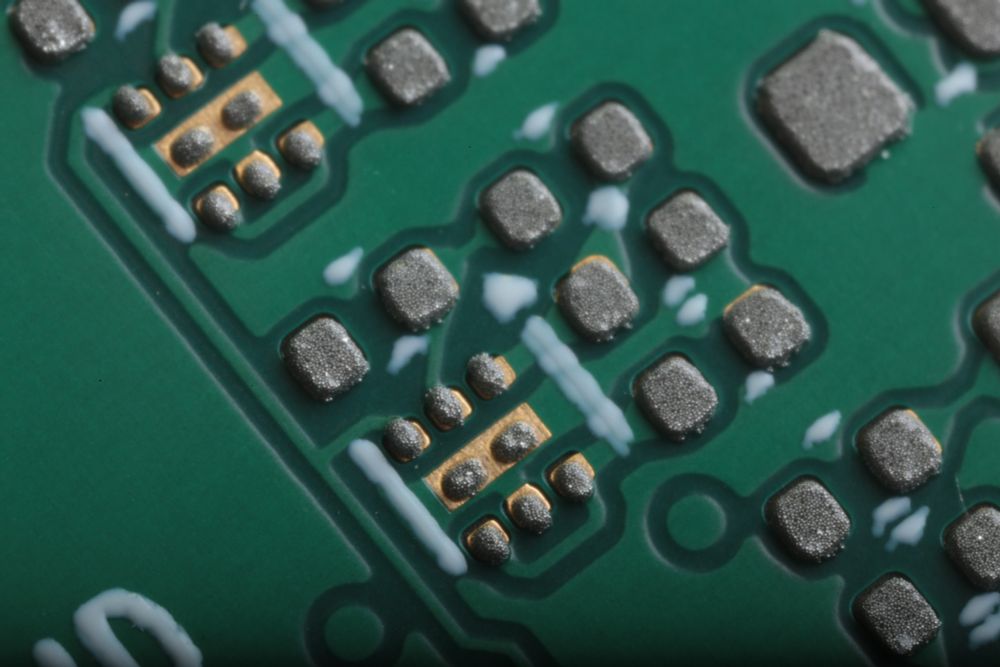

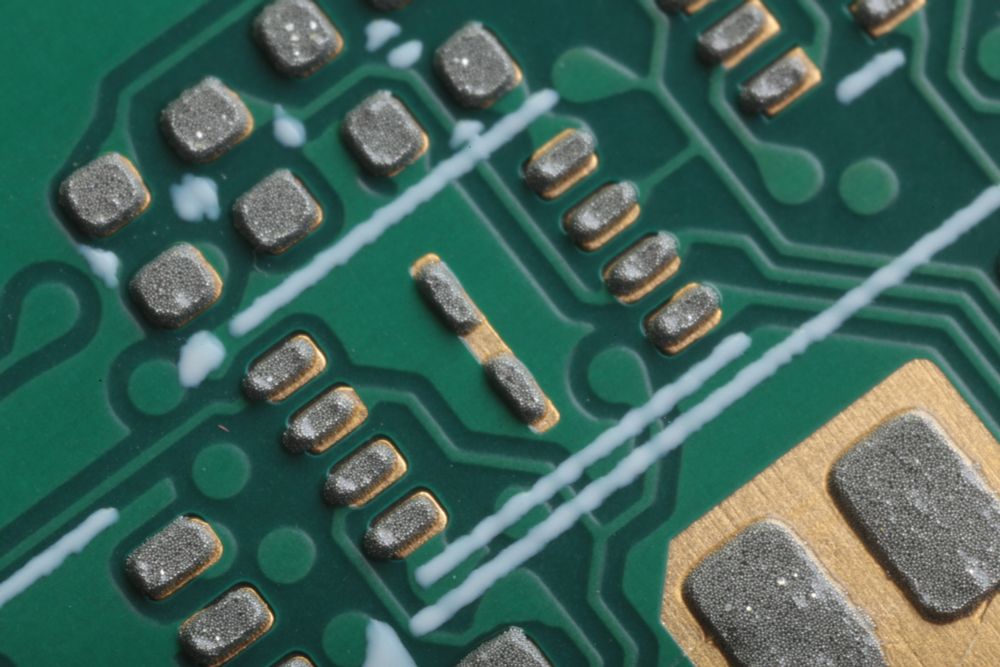

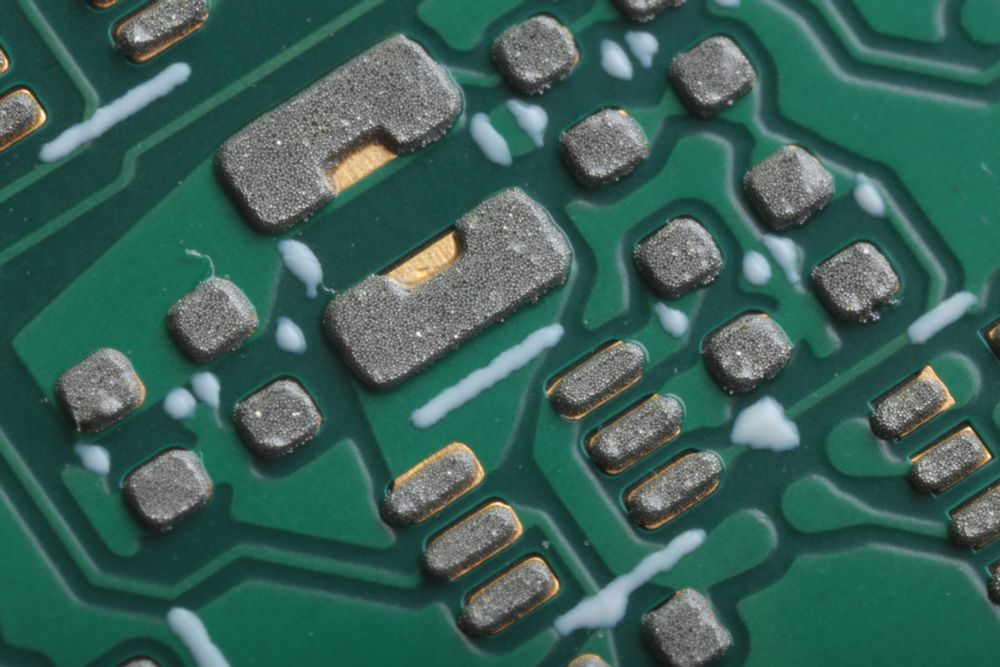

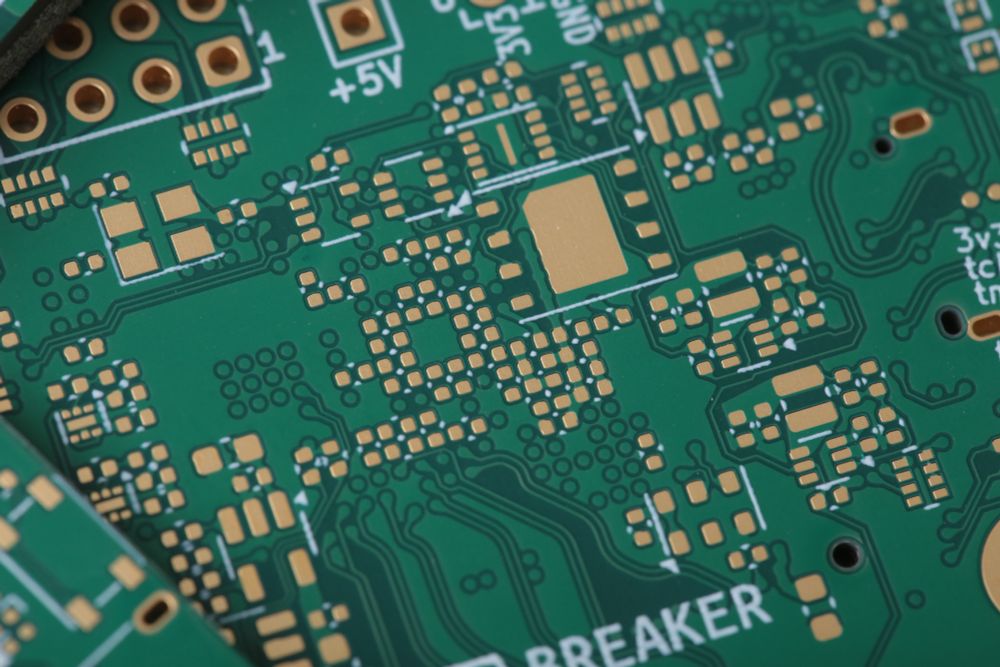

I also take macro photos of electronics

Bodge wire to the rescue! Now we're enumerating again!

USB boot loader in gateware, takes up ~15% of the device

Bodge wire to the rescue! Now we're enumerating again!

USB boot loader in gateware, takes up ~15% of the device

Makes for an interesting visual effect.

Makes for an interesting visual effect.

I think I missed some spots. 🫣

I think I missed some spots. 🫣

A DFF in front of the ECP5's FPGA SPI configuration port before a mix leading to FLASH and PSRAM. Enabling an initial jump through FLASH where the clock frequency is bumped and QSPI entered.

This now fixes an issue violating the PSRAM's tCE<8us requirement.

A DFF in front of the ECP5's FPGA SPI configuration port before a mix leading to FLASH and PSRAM. Enabling an initial jump through FLASH where the clock frequency is bumped and QSPI entered.

This now fixes an issue violating the PSRAM's tCE<8us requirement.

The messier the plan the cleaner the bodge looks in comparison. 😅

The messier the plan the cleaner the bodge looks in comparison. 😅

I guess it makes sense.. But still puzzled me for a moment that you can perform a vertical/horizontal mirror on a single cell. 🙃

I guess it makes sense.. But still puzzled me for a moment that you can perform a vertical/horizontal mirror on a single cell. 🙃

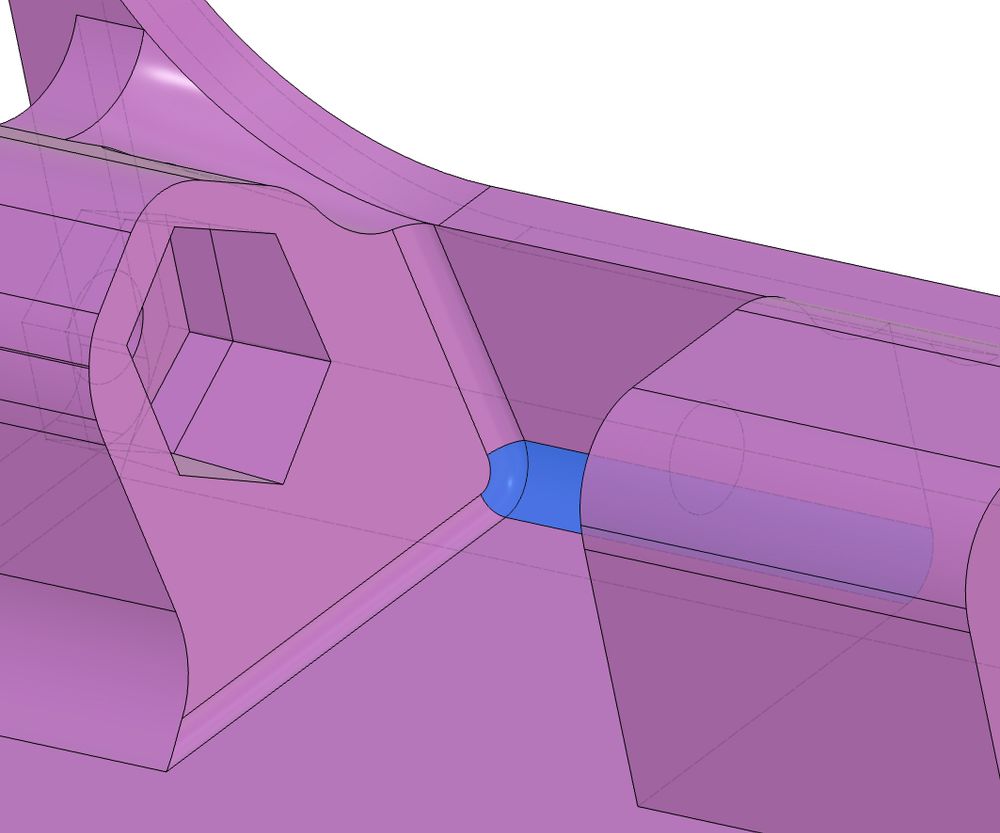

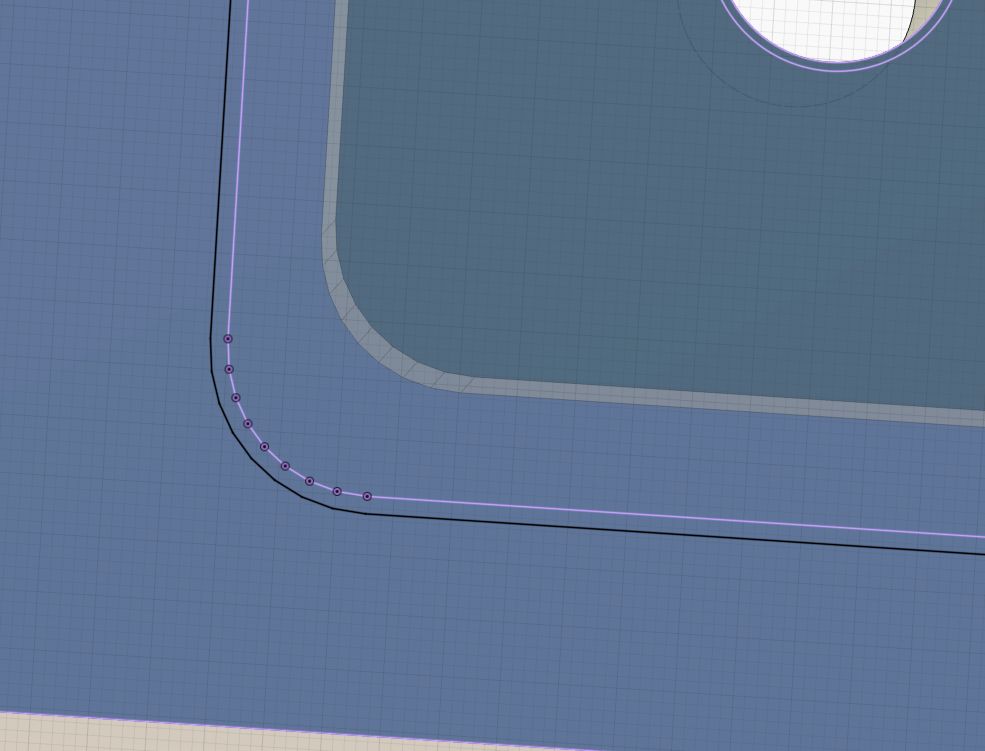

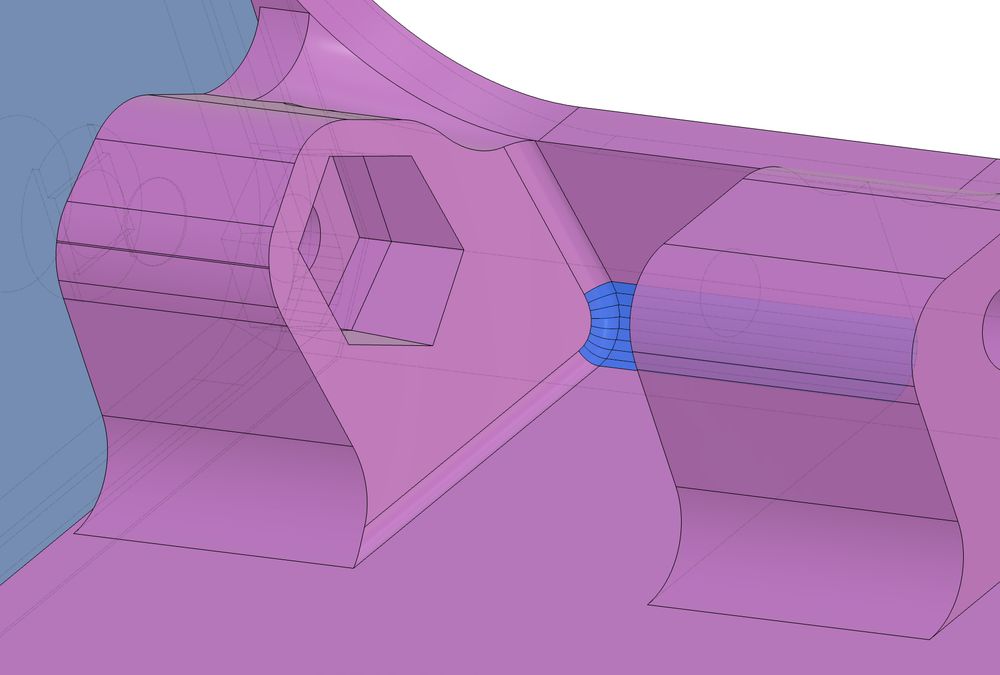

Top object is an imported PCB, arcs on the board outline get converted to straight-line segments when it's exported from KiCad.

The purple lines are projected from this PCB outline. Then I've applied an offset to account for tolerance.

Top object is an imported PCB, arcs on the board outline get converted to straight-line segments when it's exported from KiCad.

The purple lines are projected from this PCB outline. Then I've applied an offset to account for tolerance.

github.com/gregdavill/a...

github.com/gregdavill/a...

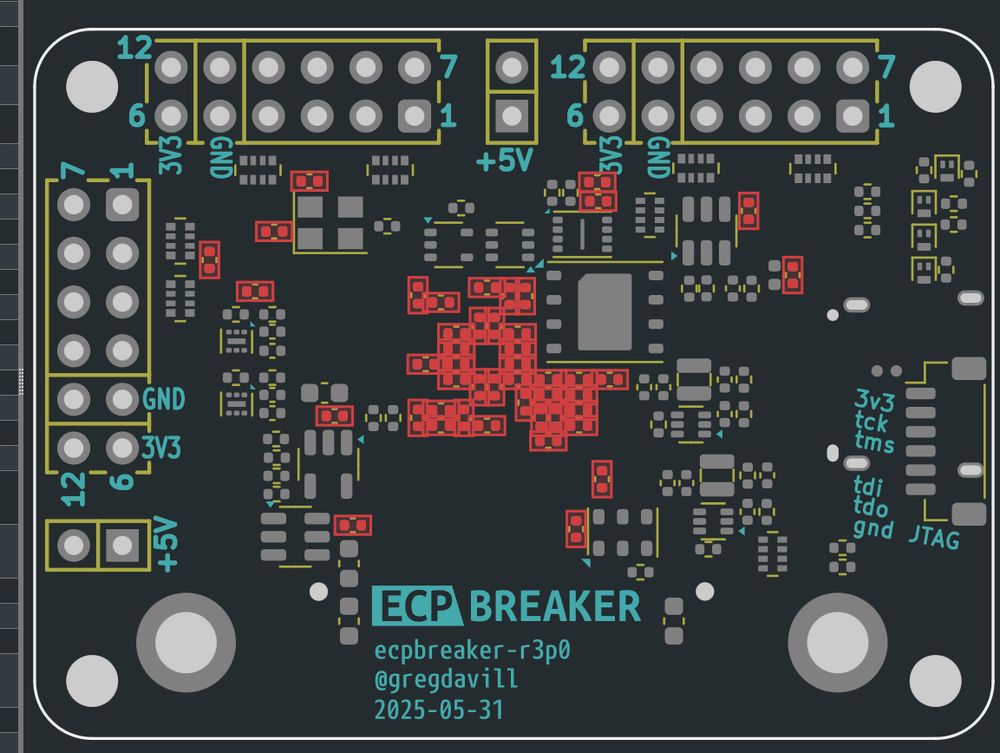

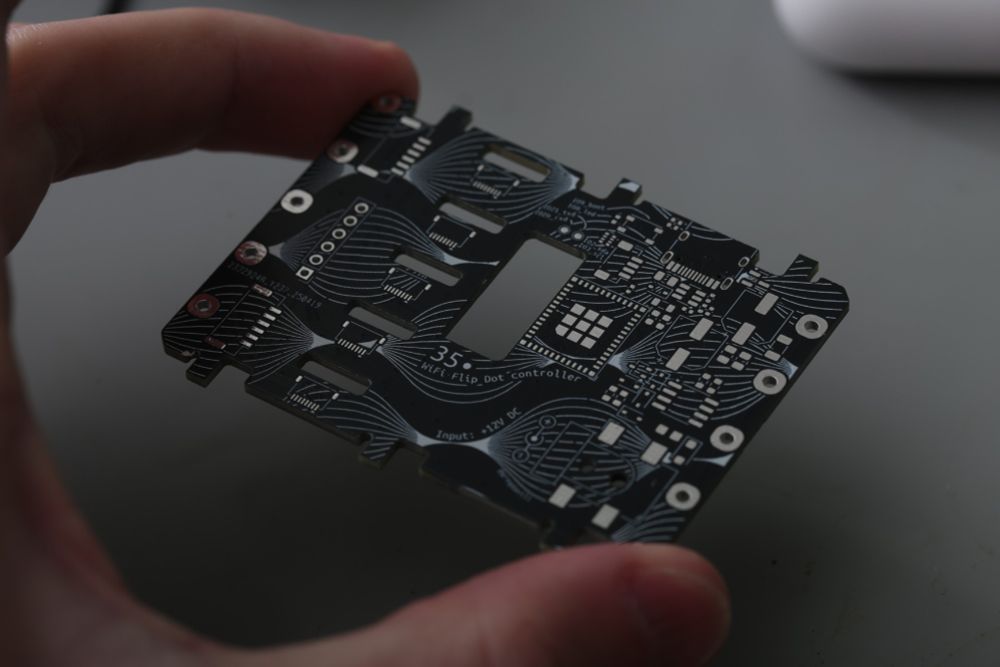

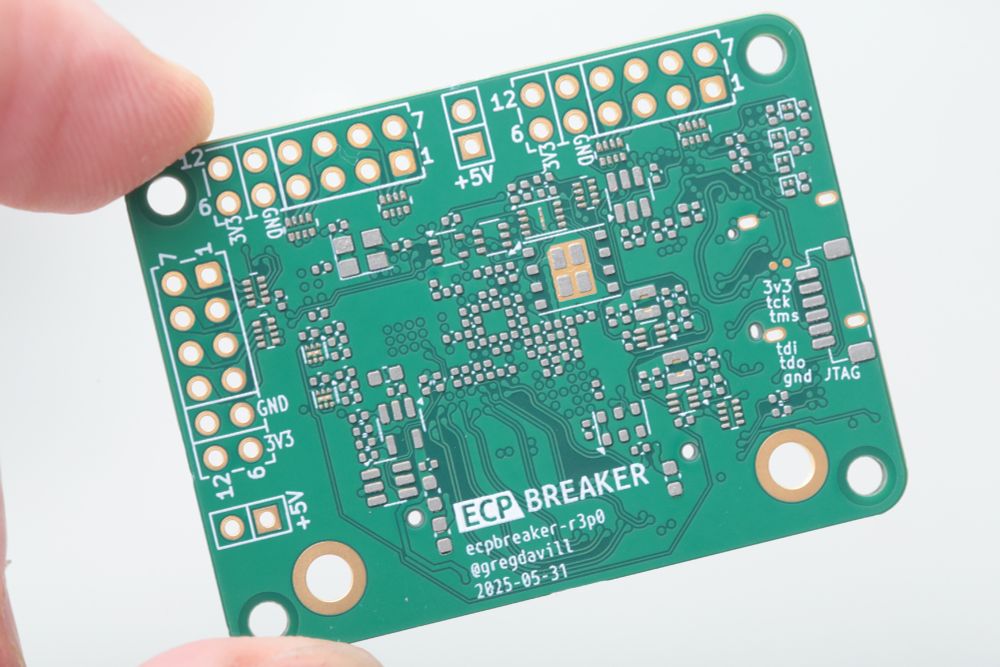

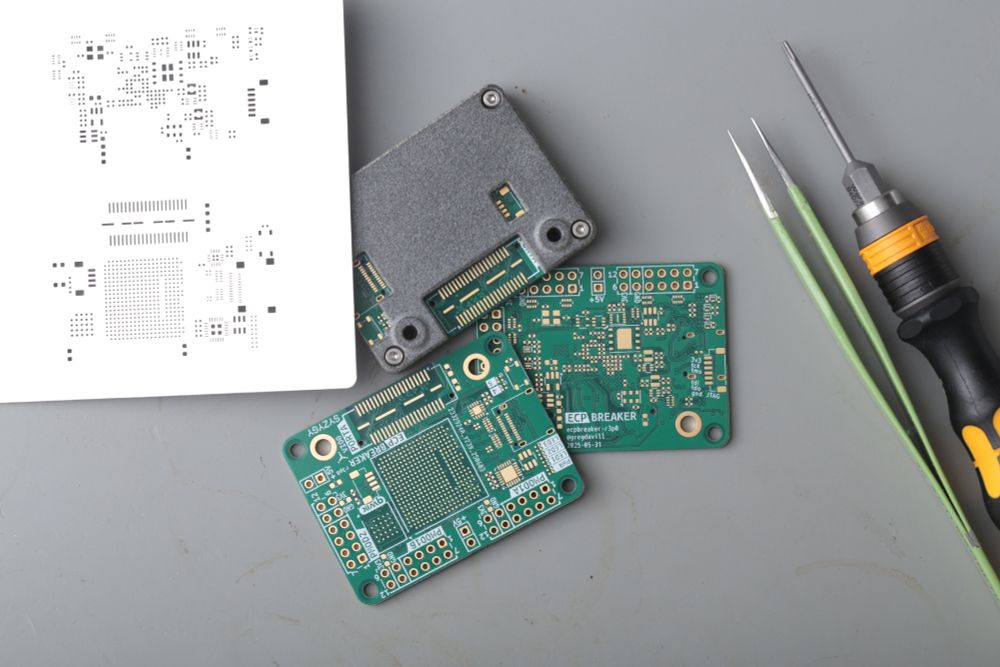

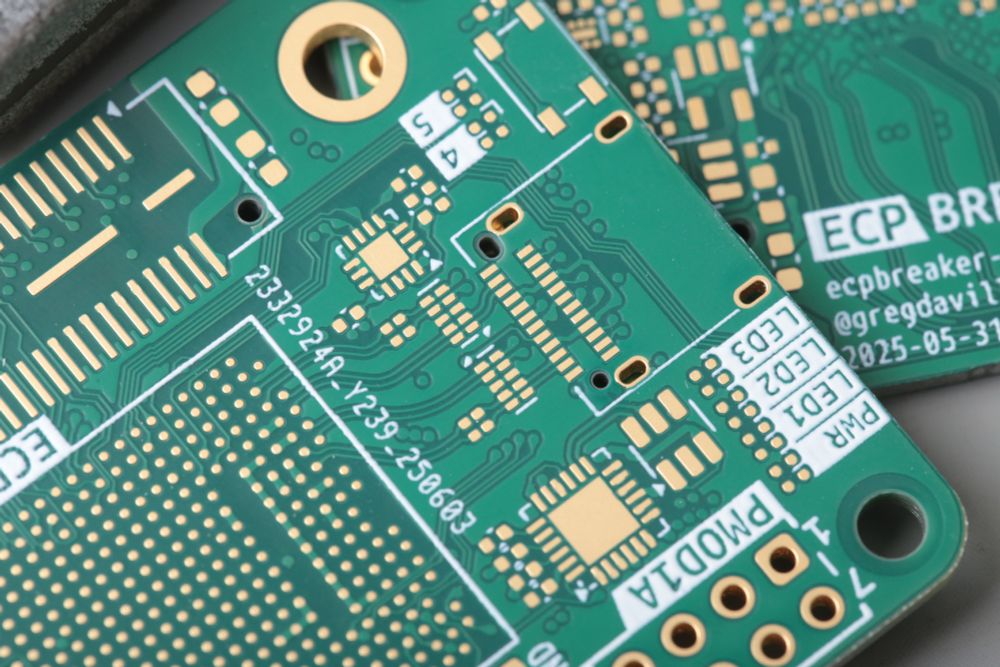

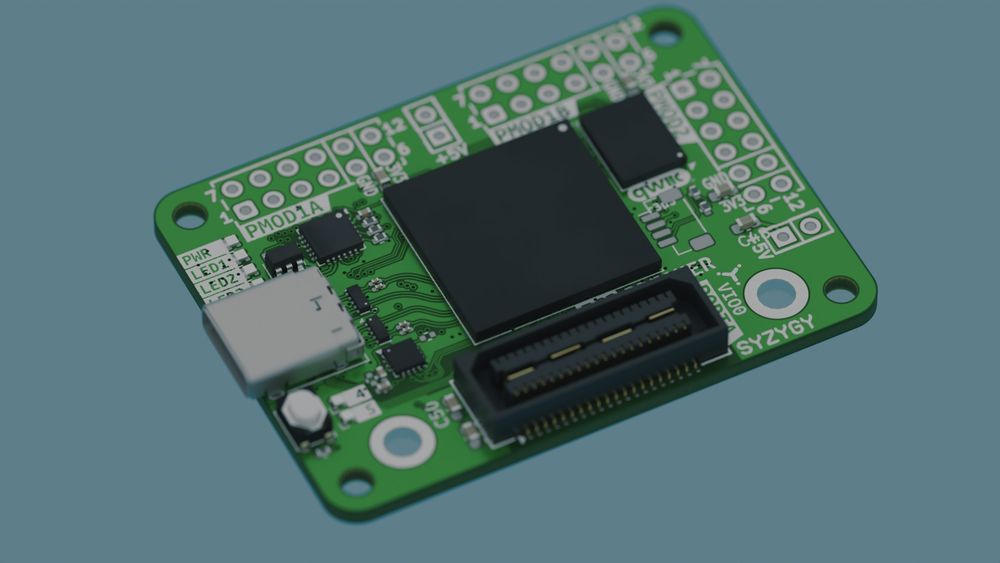

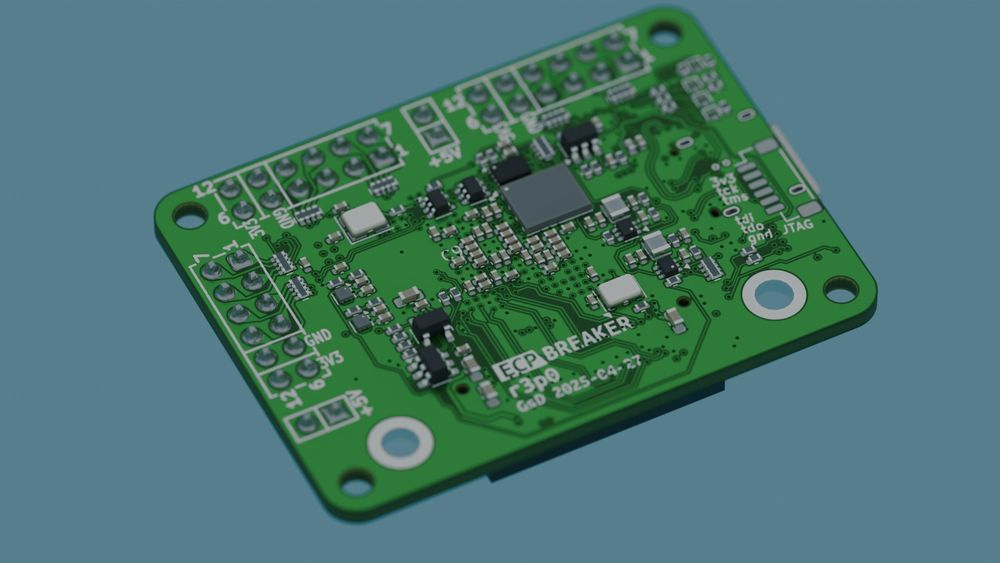

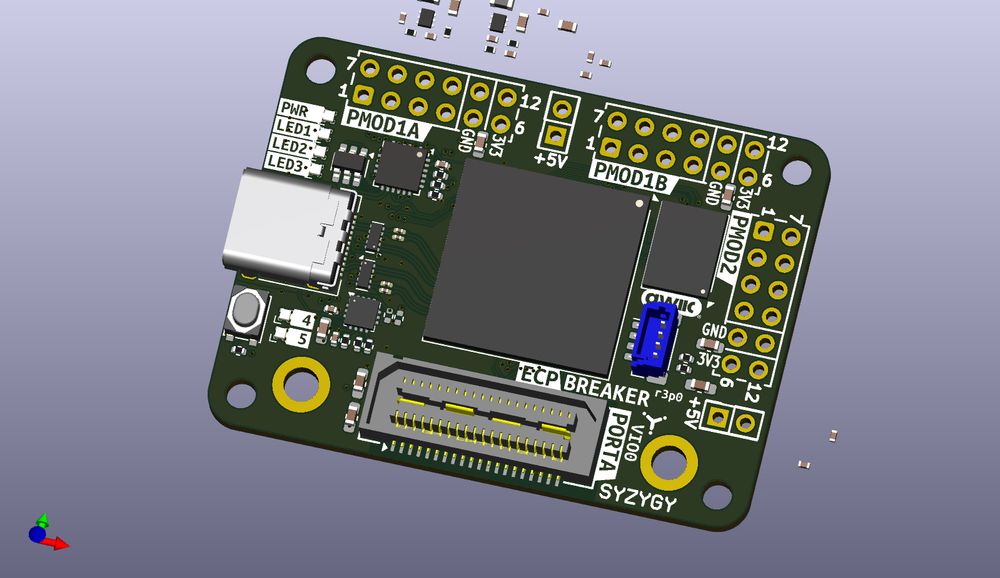

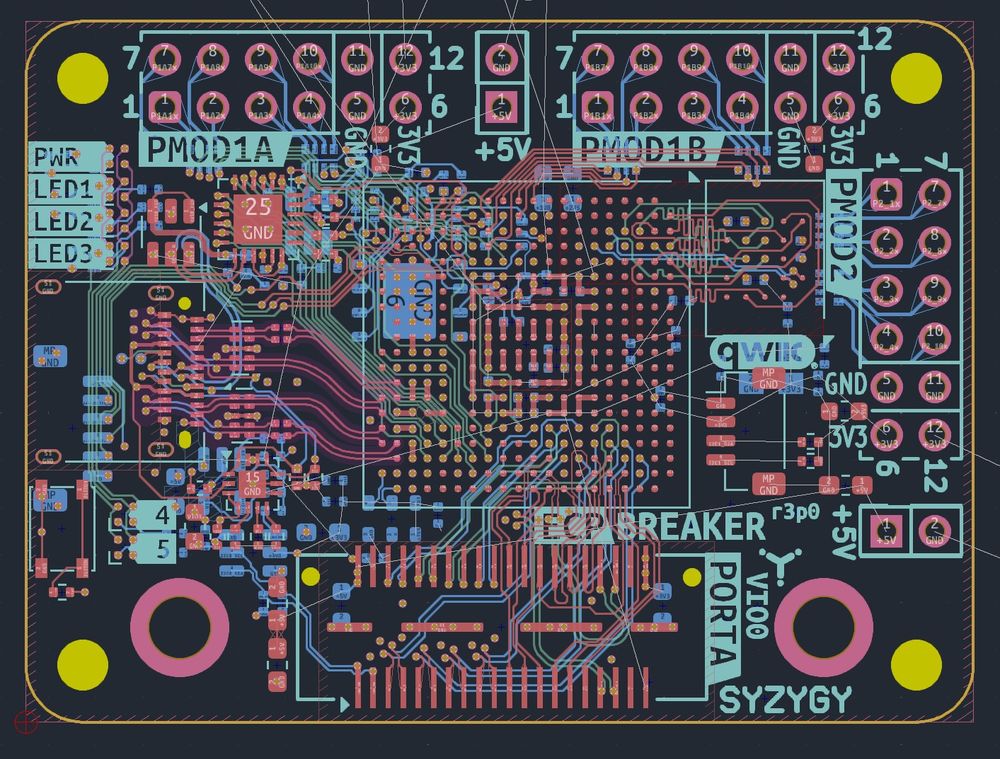

Same sized FPGA as the Butterstick, but on a board less than half the size

Same sized FPGA as the Butterstick, but on a board less than half the size

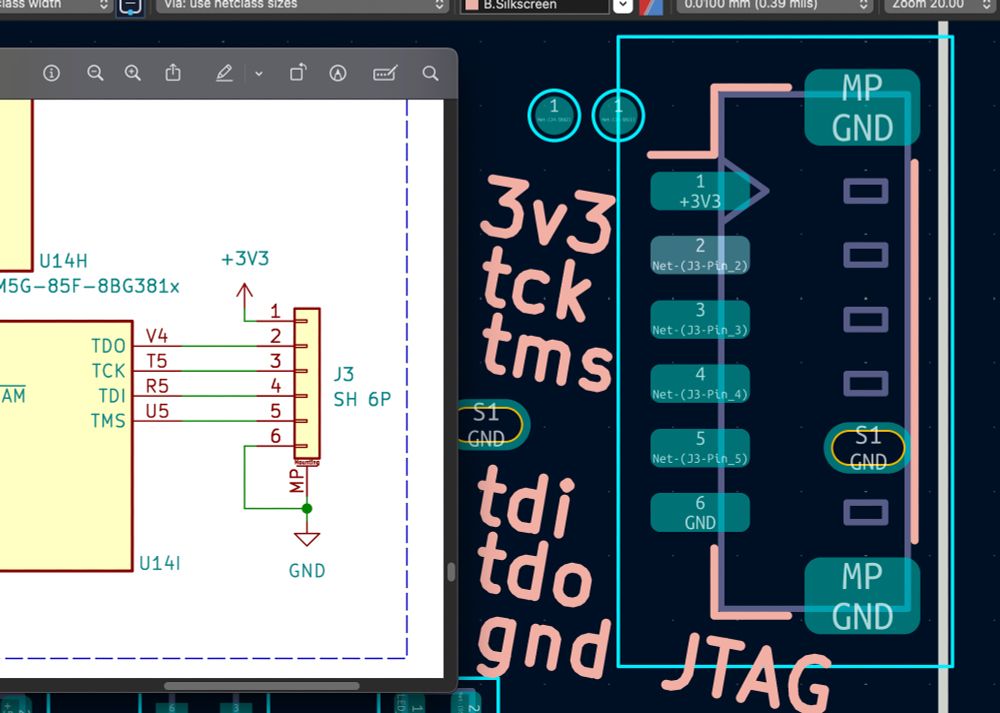

Similar idea to the last ecpbreaker design, but adding the 5Gbps SERDES to enable USB3. The ECP5's serdes supports display-port, so you could probably do some cool alt-mode stuff, but currently only routed for SS USB.

Similar idea to the last ecpbreaker design, but adding the 5Gbps SERDES to enable USB3. The ECP5's serdes supports display-port, so you could probably do some cool alt-mode stuff, but currently only routed for SS USB.

Got a little carried away in inkscape for the silkscreen.

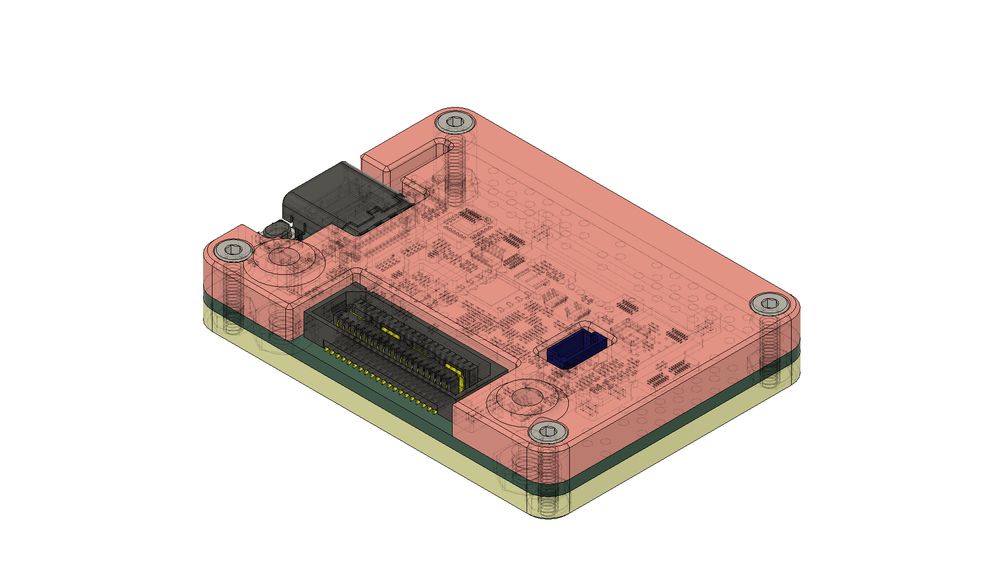

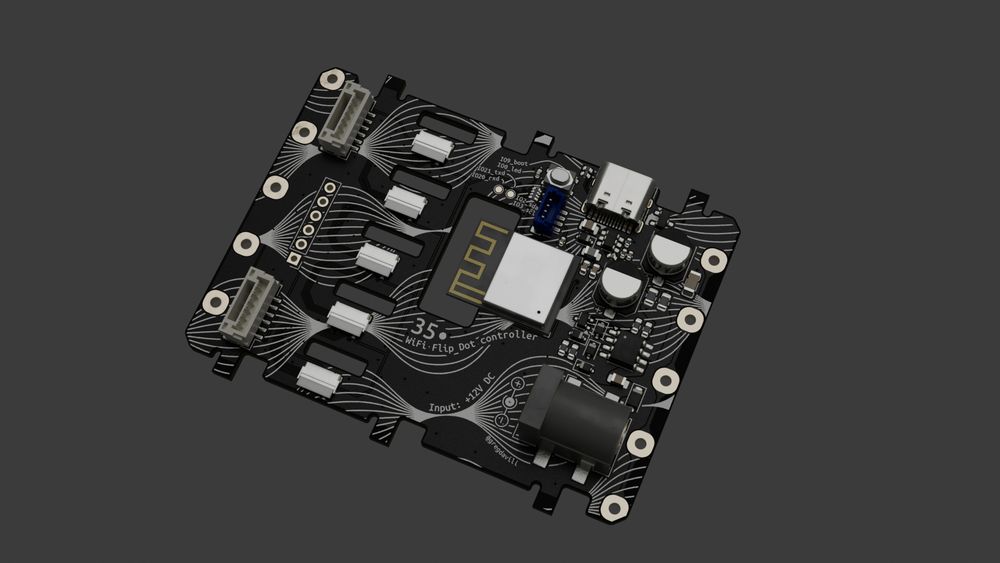

Trying out github.com/30350n/pcb2b..., a plugin that is in the KiCad PCM for exporting textures directly into blender, works great

Got a little carried away in inkscape for the silkscreen.

Trying out github.com/30350n/pcb2b..., a plugin that is in the KiCad PCM for exporting textures directly into blender, works great