I have been writing code since 1986.

Budapest, Europe

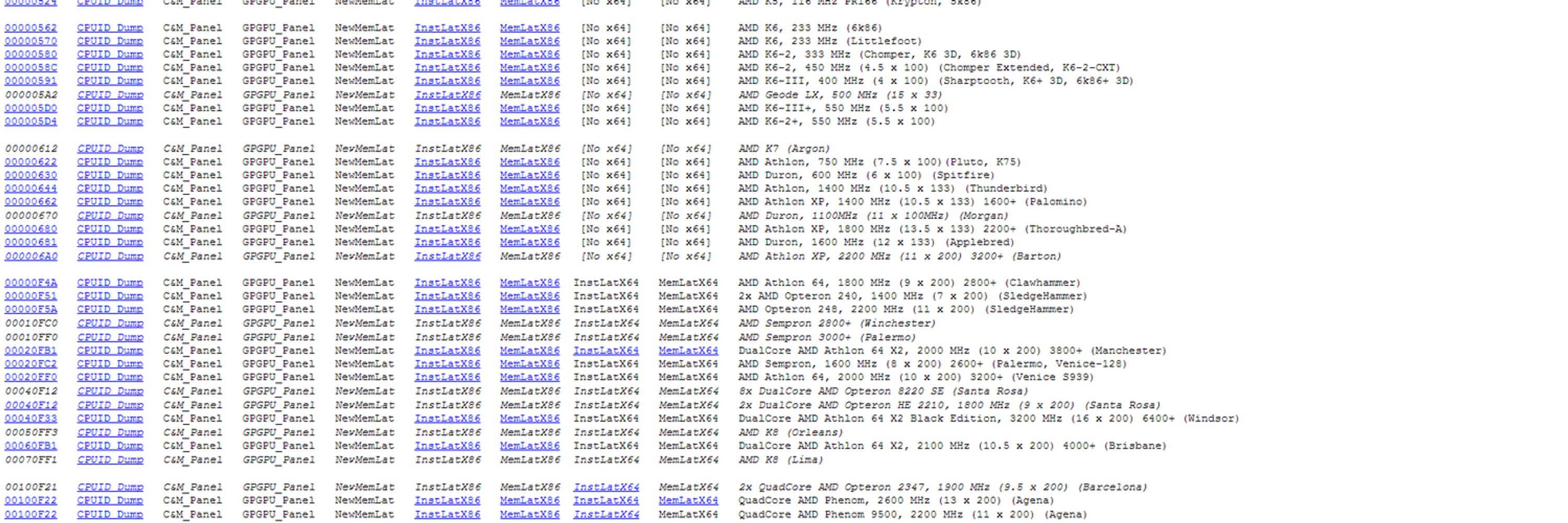

https://instlatx64.github.io/InstLatx64/

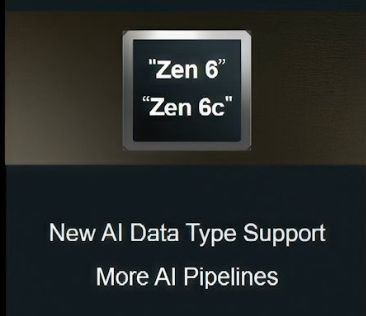

What can means DFMA here?

What can means DFMA here?

VPTERNLOG[B,W] - how useful would be this! e.g. byte granularity, single-uop (mask)?0:(c?a:b)

Source:

www.sandpile.org/x86/opc_3.htm

3/3

VPTERNLOG[B,W] - how useful would be this! e.g. byte granularity, single-uop (mask)?0:(c?a:b)

Source:

www.sandpile.org/x86/opc_3.htm

3/3

VPLZCNT[B,W] - the missing byte & word LZCNT

VPTZCNT[B,W,D,Q] - Analogous to LZCNT[B,W,D,Q]

VPADD[,U]S[D,Q] - saturated signed / unsigned addition for dword / qword (but why there isn't VPSUB[,U]S[D,Q]?)

2/3

VPLZCNT[B,W] - the missing byte & word LZCNT

VPTZCNT[B,W,D,Q] - Analogous to LZCNT[B,W,D,Q]

VPADD[,U]S[D,Q] - saturated signed / unsigned addition for dword / qword (but why there isn't VPSUB[,U]S[D,Q]?)

2/3