but the opam repo isn't just a database - it's a comprehensive CI system testing packages across 5+ OS platforms and multiple architectures (even RISC-V and PowerPC!). it ensures quality through both automation and human review 🔥

November 5, 2025 at 9:44 PM

but the opam repo isn't just a database - it's a comprehensive CI system testing packages across 5+ OS platforms and multiple architectures (even RISC-V and PowerPC!). it ensures quality through both automation and human review 🔥

This is going way over my head, but still cool to see that the RISC-V organization doesn't forget about gaming.

youtu.be/S_NkVBgOcoQ

youtu.be/S_NkVBgOcoQ

RISC-V for Gaming: Emulating X86 on RISC-V - Paris Oplopoios, felix86

YouTube video by RISC-V International

youtu.be

November 5, 2025 at 6:41 PM

This is going way over my head, but still cool to see that the RISC-V organization doesn't forget about gaming.

youtu.be/S_NkVBgOcoQ

youtu.be/S_NkVBgOcoQ

Interesting that having to emulate paging via softmmu and 80-bit x87 floats are what kills copy.sh/v86 wasm-based JIT performance. I wonder how fast you could go with MMU-less RISC-V Linux? Could be nice for non-jailbroken iOS.

v86

Run KolibriOS, Linux or Windows 98 in your browser

copy.sh

November 6, 2025 at 9:57 PM

Interesting that having to emulate paging via softmmu and 80-bit x87 floats are what kills copy.sh/v86 wasm-based JIT performance. I wonder how fast you could go with MMU-less RISC-V Linux? Could be nice for non-jailbroken iOS.

the reason for this seems to be, that a lot of time is spent effectively single-threaded in guile ("guild compile"). RISC-V cores' single-thread performance doesn't tend to be their strongest point

November 9, 2025 at 4:07 PM

the reason for this seems to be, that a lot of time is spent effectively single-threaded in guile ("guild compile"). RISC-V cores' single-thread performance doesn't tend to be their strongest point

I hope to build a RISC-V powered arcade cabinet someday 🤞

November 5, 2025 at 7:08 PM

I hope to build a RISC-V powered arcade cabinet someday 🤞

RISC-Vの命令セットがISO/IEC JTC1による国際標準化に着手へ。第一歩として公開仕様提出者の承認を受ける

https://www.publickey1.jp/blog/25/risc-visoiet_jtc1.html

https://www.publickey1.jp/blog/25/risc-visoiet_jtc1.html

RISC-Vの命令セットがISO/IEC JTC1による国際標準化に着手へ。第一歩として公開仕様提出者の承認を受ける

RISC-V(リスクファイブ)は、クリエイティブコモンズとして公開され、誰でも無料で利用可能なプロセッサの命令セットです。近年ではx86やArmに次ぐ命令セットとして注目度が高まっています。 RISC-Vを主導する団体RISC-V Inte...

www.publickey1.jp

November 5, 2025 at 11:34 PM

RISC-Vの命令セットがISO/IEC JTC1による国際標準化に着手へ。第一歩として公開仕様提出者の承認を受ける

https://www.publickey1.jp/blog/25/risc-visoiet_jtc1.html

https://www.publickey1.jp/blog/25/risc-visoiet_jtc1.html

NEWS! Due to an influx of requests we at the Rust Foundation have heard your pleas and are proud to announce rust-v! A new risc architecture with modern features such as:

- Hardware support for Rc/RefCell

- Unicode support at the instruction level

- optimizations the borrow checker can take […]

- Hardware support for Rc/RefCell

- Unicode support at the instruction level

- optimizations the borrow checker can take […]

Original post on mastodon.social

mastodon.social

November 8, 2025 at 12:08 AM

NEWS! Due to an influx of requests we at the Rust Foundation have heard your pleas and are proud to announce rust-v! A new risc architecture with modern features such as:

- Hardware support for Rc/RefCell

- Unicode support at the instruction level

- optimizations the borrow checker can take […]

- Hardware support for Rc/RefCell

- Unicode support at the instruction level

- optimizations the borrow checker can take […]

github.com/BrunoLevy/le... has just reached 3000 stars on github.

What is it ? a hand-on tutorial to learn processor design with FPGAs.

In a couple of evenings, you will create a full-fledged Risc-V.

Why would I want to do that ? Why not !!

What is it ? a hand-on tutorial to learn processor design with FPGAs.

In a couple of evenings, you will create a full-fledged Risc-V.

Why would I want to do that ? Why not !!

October 31, 2025 at 3:56 PM

github.com/BrunoLevy/le... has just reached 3000 stars on github.

What is it ? a hand-on tutorial to learn processor design with FPGAs.

In a couple of evenings, you will create a full-fledged Risc-V.

Why would I want to do that ? Why not !!

What is it ? a hand-on tutorial to learn processor design with FPGAs.

In a couple of evenings, you will create a full-fledged Risc-V.

Why would I want to do that ? Why not !!

I got a request to make an PURE Assembler driver in RISC-V so here it is. No SDK as it will teach you the basics of a RISC-V chip specifically the ESP32-C3. #Embedded #ReverseEngineering github.com/mytechnotale...

November 1, 2025 at 7:35 PM

I got a request to make an PURE Assembler driver in RISC-V so here it is. No SDK as it will teach you the basics of a RISC-V chip specifically the ESP32-C3. #Embedded #ReverseEngineering github.com/mytechnotale...

Tengo SuperH, ARM, X86, MIPS, PowerPC, RISC-V, ALPHA y no sé si se me olvida alguno más?

November 1, 2025 at 12:46 PM

Tengo SuperH, ARM, X86, MIPS, PowerPC, RISC-V, ALPHA y no sé si se me olvida alguno más?

Setting up a risc-v sbc has been fun so far. One step with be to install box64

November 1, 2025 at 12:41 AM

Setting up a risc-v sbc has been fun so far. One step with be to install box64

raylib running on RISC-V board, Orange Pi RV2, using Mesa llvmpipe software renderer backend, getting ~300 sprites @ 30fps.

Next: try new raylib rlsw software renderer and RVV extension... 🔥👍😄

Next: try new raylib rlsw software renderer and RVV extension... 🔥👍😄

October 29, 2025 at 11:48 AM

raylib running on RISC-V board, Orange Pi RV2, using Mesa llvmpipe software renderer backend, getting ~300 sprites @ 30fps.

Next: try new raylib rlsw software renderer and RVV extension... 🔥👍😄

Next: try new raylib rlsw software renderer and RVV extension... 🔥👍😄

Thank you RISC-V International for an incredible #RISCVSummit! Great to connect with our ecosystem partners, BrainChip, Arteris, Baya Systems, proteanTecs & S2C EDA, and share Andes innovations in AI, security & next-gen RISC-V CPU IP.

#RISCV #RISCVEverywhere

#RISCV #RISCVEverywhere

October 30, 2025 at 9:49 PM

Thank you RISC-V International for an incredible #RISCVSummit! Great to connect with our ecosystem partners, BrainChip, Arteris, Baya Systems, proteanTecs & S2C EDA, and share Andes innovations in AI, security & next-gen RISC-V CPU IP.

#RISCV #RISCVEverywhere

#RISCV #RISCVEverywhere

(Before everybody gets excited and asks for my OnlyFans page, I put a RISC-V soft core onto an FPGA.)

October 30, 2025 at 6:33 AM

(Before everybody gets excited and asks for my OnlyFans page, I put a RISC-V soft core onto an FPGA.)

Want a fast, simple, and small integer FFT implementation geared for 32-bit (ARM + RISC-V) processors? I have largely rewritten one of the more popular fix_fft implementations and got the OK by most recent maintainers to put it under the MIT license. github.com/cnlohr/fix32...

GitHub - cnlohr/fix32_fft: Header-only C fixed-point FFT library for embedded and specialty situations

Header-only C fixed-point FFT library for embedded and specialty situations - cnlohr/fix32_fft

github.com

October 29, 2025 at 7:33 AM

Want a fast, simple, and small integer FFT implementation geared for 32-bit (ARM + RISC-V) processors? I have largely rewritten one of the more popular fix_fft implementations and got the OK by most recent maintainers to put it under the MIT license. github.com/cnlohr/fix32...

Bolt Graphics unveils Zeus GPU built on RISC-V and path tracing tech

Bolt Graphics unveils Zeus GPU built on RISC-V and path tracing tech

Onboard cores use a Linux stack based on Ubuntu

Ubuntu Summit One of the more unexpected talks at last week's Ubuntu Summit 25.10 in London was by Antonio Salvemini of Bolt Graphics, who introduced the company's forthcoming range of Zeus graphics accelerator hardware. These are very unlike any conventional GPUs – or indeed anything else.…

dlvr.it

October 29, 2025 at 10:43 AM

Bolt Graphics unveils Zeus GPU built on RISC-V and path tracing tech

I designed a thing!

It's a CPU module for a possible RISC-V hackable computer.

It's a CPU module for a possible RISC-V hackable computer.

October 27, 2025 at 10:57 PM

I designed a thing!

It's a CPU module for a possible RISC-V hackable computer.

It's a CPU module for a possible RISC-V hackable computer.

Easy RISC-V

Easy RISC-V

dramforever.github.io

October 27, 2025 at 11:30 PM

This idea for a RISC-V machine similar to RC2014 seemed like a good one so I've been thinking about it for the last few days.

I've put together a rough plan for how it might be done - I'm interested in what people think!

github.com/MichaelBell/...

I've put together a rough plan for how it might be done - I'm interested in what people think!

github.com/MichaelBell/...

October 25, 2025 at 5:02 PM

This idea for a RISC-V machine similar to RC2014 seemed like a good one so I've been thinking about it for the last few days.

I've put together a rough plan for how it might be done - I'm interested in what people think!

github.com/MichaelBell/...

I've put together a rough plan for how it might be done - I'm interested in what people think!

github.com/MichaelBell/...

Until the original repository accepts my changes, you can find my improved version of this handy "building for WCH chips" script here.

github.com/mikekasprzak...

Once you install a few tools (a RISC-V GCC, wlink, wchisp), it's everything you need to write software in C/C++ for these chips.

github.com/mikekasprzak...

Once you install a few tools (a RISC-V GCC, wlink, wchisp), it's everything you need to write software in C/C++ for these chips.

GitHub - mikekasprzak/ch32v_evt_makefile_gcc_project_template: gcc makefile project template and convertor for WCH CH32V EVT packages

gcc makefile project template and convertor for WCH CH32V EVT packages - GitHub - mikekasprzak/ch32v_evt_makefile_gcc_project_template: gcc makefile project template and convertor for WCH CH32V EV...

github.com

October 25, 2025 at 5:21 PM

Until the original repository accepts my changes, you can find my improved version of this handy "building for WCH chips" script here.

github.com/mikekasprzak...

Once you install a few tools (a RISC-V GCC, wlink, wchisp), it's everything you need to write software in C/C++ for these chips.

github.com/mikekasprzak...

Once you install a few tools (a RISC-V GCC, wlink, wchisp), it's everything you need to write software in C/C++ for these chips.

StarFive released a new custom Debian image for the VisionFive 2 and VisionFive 2 Lite RISC-V SBCs.

forum.rvspace.org/t/visionfive...

forum.rvspace.org/t/visionfive...

VisionFive 2 (Lite) Debian 202510 Released

👍 😍 🌹

forum.rvspace.org

October 24, 2025 at 8:41 AM

StarFive released a new custom Debian image for the VisionFive 2 and VisionFive 2 Lite RISC-V SBCs.

forum.rvspace.org/t/visionfive...

forum.rvspace.org/t/visionfive...

"I am a software guy. So I earned all my money with software, and lost all my money with hardware" 💀

Yuning Liang, is unhinged at #UbuntuSummit2510 talking about the rise of RISC-V

#UbuntuSummit

Yuning Liang, is unhinged at #UbuntuSummit2510 talking about the rise of RISC-V

#UbuntuSummit

October 24, 2025 at 9:45 AM

"I am a software guy. So I earned all my money with software, and lost all my money with hardware" 💀

Yuning Liang, is unhinged at #UbuntuSummit2510 talking about the rise of RISC-V

#UbuntuSummit

Yuning Liang, is unhinged at #UbuntuSummit2510 talking about the rise of RISC-V

#UbuntuSummit

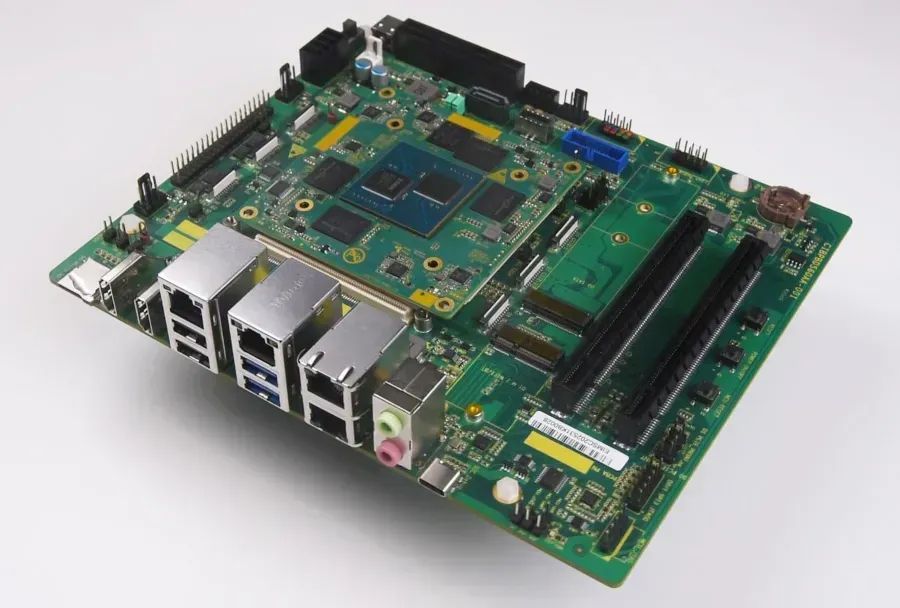

🦾 ESWIN Launching EBC7702 Mini-DTX RISC-V Board With Dual-Die EIC7702X SoC - Phoronix

#riscv #opensource

#riscv #opensource

ESWIN Launching EBC7702 Mini-DTX RISC-V Board With Dual-Die EIC7702X SoC

For those looking for a new RISC-V desktop option, ESWIN is launching a EBC7702 mini-DTX board powered by the EIC7702X dual-die SoC

www.phoronix.com

October 23, 2025 at 7:01 PM

🦾 ESWIN Launching EBC7702 Mini-DTX RISC-V Board With Dual-Die EIC7702X SoC - Phoronix

#riscv #opensource

#riscv #opensource

💥 Boom - Technology Launch!

bit.ly/3JiVOLm

We’ve shared #Maverick2 performance numbers for HPCG, GUPS, and PageRank — and unveiled Arbel, our enterprise-grade RISC-V core.

More (or should that be Moore 😉) 👉 nextsilicon.com

#HPC #RISC-V

Jack — thanks for your #HPCG encouragement back at #SCA25 🙌

bit.ly/3JiVOLm

We’ve shared #Maverick2 performance numbers for HPCG, GUPS, and PageRank — and unveiled Arbel, our enterprise-grade RISC-V core.

More (or should that be Moore 😉) 👉 nextsilicon.com

#HPC #RISC-V

Jack — thanks for your #HPCG encouragement back at #SCA25 🙌

October 22, 2025 at 7:52 PM

💥 Boom - Technology Launch!

bit.ly/3JiVOLm

We’ve shared #Maverick2 performance numbers for HPCG, GUPS, and PageRank — and unveiled Arbel, our enterprise-grade RISC-V core.

More (or should that be Moore 😉) 👉 nextsilicon.com

#HPC #RISC-V

Jack — thanks for your #HPCG encouragement back at #SCA25 🙌

bit.ly/3JiVOLm

We’ve shared #Maverick2 performance numbers for HPCG, GUPS, and PageRank — and unveiled Arbel, our enterprise-grade RISC-V core.

More (or should that be Moore 😉) 👉 nextsilicon.com

#HPC #RISC-V

Jack — thanks for your #HPCG encouragement back at #SCA25 🙌